- 您现在的位置:买卖IC网 > PDF目录15503 > LTC3823IGN#PBF (Linear Technology)IC REG CTRLR BUCK PWM CM 28-SSOP PDF资料下载

参数资料

| 型号: | LTC3823IGN#PBF |

| 厂商: | Linear Technology |

| 文件页数: | 18/26页 |

| 文件大小: | 0K |

| 描述: | IC REG CTRLR BUCK PWM CM 28-SSOP |

| 标准包装: | 49 |

| PWM 型: | 电流模式 |

| 输出数: | 1 |

| 频率 - 最大: | 1MHz |

| 占空比: | 90% |

| 电源电压: | 4.5 V ~ 36 V |

| 降压: | 是 |

| 升压: | 无 |

| 回扫: | 无 |

| 反相: | 无 |

| 倍增器: | 无 |

| 除法器: | 无 |

| Cuk: | 无 |

| 隔离: | 无 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 28-SSOP(0.154",3.90mm 宽) |

| 包装: | 管件 |

| 产品目录页面: | 1336 (CN2011-ZH PDF) |

�� �

�

�

�LTC3823�

�APPLICATIONS� INFORMATION�

�Differential� Ampli?er�

�R� LP�

�This� ampli?er� provides� true� differential� output� voltage�

�sensing.� Sensing� both� the� positive� and� negative� terminals�

�of� the� output� voltage� bene?ts� regulation� in� high� current�

�2.4V�

�PLLFLTR�

�C� LP�

�applications� and/or� applications� having� electrical� intercon-�

�nection� losses.� Precision� feedback� resistors� are� integrated�

�in� the� IC� with� the� ampli?er� already� con?gured� as� a� unity-gain�

�PLLIN�

�DIGITAL�

�PHASE/�

�FREQUENCY�

�DETECTOR�

�VCO�

�differential� ampli?er.� It� has� a� GBW� product� of� 3.5MHz� and�

�an� open-loop� gain� of� >120dB.� The� ampli?er� can� source�

�>2mA� of� current,� and� can� be� used� in� applications� with�

�up� to� 3.3V� output� voltage.� The� ampli?er� is� not� capable� of�

�sinking� signi?cant� current,� and� must� be� resistively� loaded.�

�A� load� of� 20k� or� less� is� recommended� for� stability.� The�

�ampli?er� is� not� designed� to� drive� capacitive� loads.�

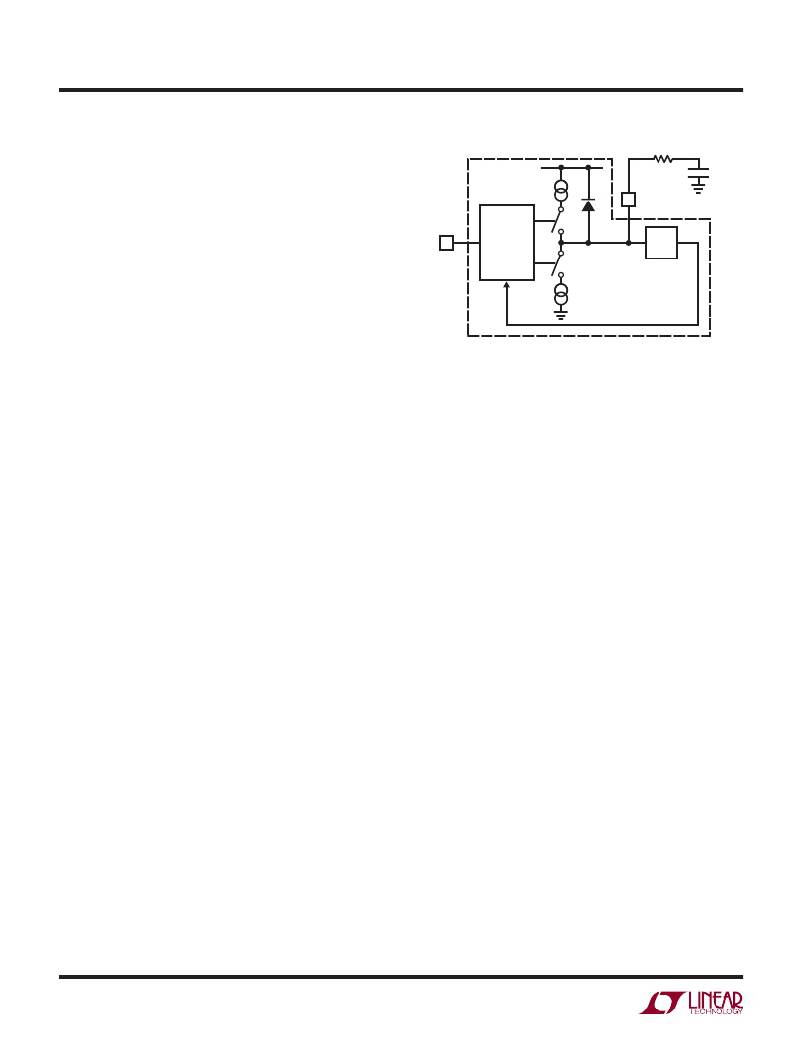

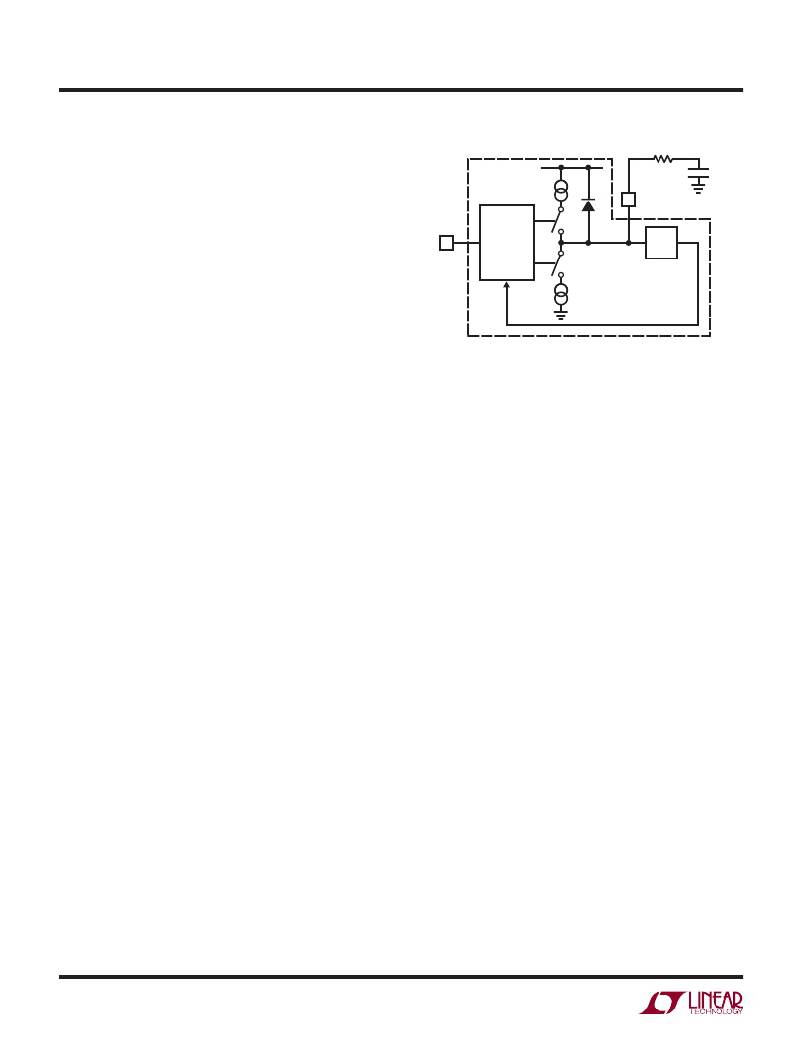

�Phase-Locked� Loop� and� Frequency� Synchronization�

�The� LTC3823� has� a� phase-locked� loop� comprised� of� an�

�internal� voltage� controlled� oscillator� and� phase� detector.�

�This� allows� the� top� MOSFET� turn-on� to� be� locked� to� the�

�rising� edge� of� an� external� source.� The� frequency� range�

�of� the� voltage� controlled� oscillator� is� ±30%� around� the�

�center� frequency,� f� O� .� The� center� frequency� is� the� operat-�

�ing� frequency� discussed� in� the� previous� section.� The�

�LTC3823� incorporates� a� pulse� detection� circuit� that� will�

�detect� a� clock� on� the� PLLIN� pin.� In� turn,� it� will� turn� on� the�

�phase-locked� loop� function.� The� pulse� width� of� the� clock�

�has� to� be� greater� than� 400ns� and� the� amplitude� of� the�

�clock� should� be� greater� than� 2V.�

�During� the� start-up� phase,� phase-locked� loop� function� is�

�disabled.� When� LTC3823� is� not� in� synchronization� mode,�

�PLLFLTR� pin� voltage� is� set� to� around� 1.18V.� Frequency�

�synchronization� is� accomplished� by� changing� the� internal�

�on-time� current� according� to� the� voltage� on� the� PLLFLTR�

�pin.�

�The� phase� detector� used� is� an� edge� sensitive� digital� type�

�which� provides� zero� degrees� phase� shift� between� the� ex-�

�ternal� and� internal� pulses.� This� type� of� phase� detector� will�

�not� lock� up� on� input� frequencies� close� to� the� harmonics�

�of� the� VCO� center� frequency.� The� PLL� hold-in� range,� Δf� H� ,�

�is� equal� to� the� capture� range,� Δf� C� :�

�Δf� H� =� Δf� C� =� ±0.3� f� O�

�3823� F10�

�Figure� 10.� Phase-Locked� Loop� Block� Diagram�

�The� output� of� the� phase� detector� is� a� complementary� pair� of�

�current� sources� charging� or� discharging� the� external� ?lter�

�network� on� the� PLLFLTR� pin.� A� simpli?ed� block� diagram�

�is� shown� in� Figure� 10.�

�If� the� external� frequency� (f� PLLIN� )� is� greater� than� the� oscil-�

�lator� frequency� f� O� ,� current� is� sourced� continuously,� pull-�

�ing� up� the� PLLFLTR� pin.� When� the� external� frequency� is�

�less� than� f� O� ,� current� is� sunk� continuously,� pulling� down�

�the� PLLFLTR� pin.� If� the� external� and� internal� frequencies�

�are� the� same� but� exhibit� a� phase� difference,� the� current�

�sources� turn� on� for� an� amount� of� time� corresponding� to�

�the� phase� difference.� Thus� the� voltage� on� the� PLLFLTR�

�pin� is� adjusted� until� the� phase� and� frequency� of� the� external�

�and� internal� oscillators� are� identical.� At� this� stable� operating�

�point� the� phase� comparator� output� is� open� and� the� ?lter�

�capacitor� C� LP� holds� the� voltage.� The� LTC3823� PLLIN� pin�

�must� be� driven� from� a� low� impedance� source� such� as� a�

�logic� gate� located� close� to� the� pin.�

�The� loop� ?lter� components� (C� LP� ,� R� LP� )� smooth� out� the� cur-�

�rent� pulses� from� the� phase� detector� and� provide� a� stable�

�input� to� the� voltage� controlled� oscillator.� The� ?lter� compo-�

�nents� C� LP� and� R� LP� determine� how� fast� the� loop� acquires�

�lock.� Typically� R� LP� =10k� and� C� LP� is� 0.01μF� to� 0.1μF.�

�Dead� Time� Control�

�To� further� optimize� the� ef?ciency,� the� LTC3823� gives� us-�

�ers� some� control� over� the� dead� time� of� the� Top� gate� low�

�and� Bottom� gate� high� transition.� By� applying� a� DC� voltage�

�on� the� Z0� pin,� the� TG� low� BG� high� dead� time� can� be� pro-�

�grammed.� Because� the� dead� time� is� a� strong� function� of�

�3823fd�

�18�

�相关PDF资料 |

PDF描述 |

|---|---|

| SPD62-682M | INDUCTOR PWR SHIELDED 6.80UH SMD |

| MIC2186YM | IC REG CTRLR BST FLYBK CM 16SOIC |

| MIC2185YM | IC REG CTRLR BST PWM CM 16-SOIC |

| MIC2184YM | IC REG CTRLR BUCK PWM CM 16-SOIC |

| SPD62-472M | INDUCTOR PWR SHIELDED 4.70UH SMD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LTC3823IUH#PBF | 功能描述:IC REG CTRLR BUCK PWM CM 32-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 特色产品:LM3753/54 Scalable 2-Phase Synchronous Buck Controllers 标准包装:1 系列:PowerWise® PWM 型:电压模式 输出数:1 频率 - 最大:1MHz 占空比:81% 电源电压:4.5 V ~ 18 V 降压:是 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:无 工作温度:-5°C ~ 125°C 封装/外壳:32-WFQFN 裸露焊盘 包装:Digi-Reel® 产品目录页面:1303 (CN2011-ZH PDF) 其它名称:LM3754SQDKR |

| LTC3823IUH#PBF | 制造商:Linear Technology 功能描述:IC SYNC STEP-DOWN DC/DC CONTROLLER QFN32 |

| LTC3823IUH#TRPBF | 功能描述:IC REG CTRLR BUCK PWM CM 32-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:500kHz 占空比:96% 电源电压:4 V ~ 36 V 降压:无 升压:是 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:无 工作温度:-40°C ~ 125°C 封装/外壳:24-WQFN 裸露焊盘 包装:带卷 (TR) |

| LTC3824EMSE | 制造商:Linear Technology 功能描述:DC DC Cntrlr Single-OUT Step Down 4V to 60V Input 10-Pin MSOP EP |

| LTC3824EMSE#PBF | 功能描述:IC REG CTRLR BUCK PWM CM 10-MSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 特色产品:LM3753/54 Scalable 2-Phase Synchronous Buck Controllers 标准包装:1 系列:PowerWise® PWM 型:电压模式 输出数:1 频率 - 最大:1MHz 占空比:81% 电源电压:4.5 V ~ 18 V 降压:是 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:无 工作温度:-5°C ~ 125°C 封装/外壳:32-WFQFN 裸露焊盘 包装:Digi-Reel® 产品目录页面:1303 (CN2011-ZH PDF) 其它名称:LM3754SQDKR |

发布紧急采购,3分钟左右您将得到回复。