- 您现在的位置:买卖IC网 > PDF目录79893 > LTC4222CUH#TRPBF (LINEAR TECHNOLOGY CORP) 2-CHANNEL POWER SUPPLY SUPPORT CKT, PQCC32 PDF资料下载

参数资料

| 型号: | LTC4222CUH#TRPBF |

| 厂商: | LINEAR TECHNOLOGY CORP |

| 元件分类: | 电源管理 |

| 英文描述: | 2-CHANNEL POWER SUPPLY SUPPORT CKT, PQCC32 |

| 封装: | 5 X 5 MM, LEAD FREE, PLASTIC, MO-220WHHD-X, QFN-32 |

| 文件页数: | 9/32页 |

| 文件大小: | 280K |

| 代理商: | LTC4222CUH#TRPBF |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

LTC4222

17

4222fa

APPLICATIONS INFORMATION

Setting the CONFIG pin high allows the two channels to

start up and turn off independently. When both ON signals

are brought high sequentially, the channel turned on rst

immediately begins to start up and the second channel

has a 200ns window to assert it’s ON signal in order to

start up in the same timer period. If the second ON signal

is asserted after the 200ns window but before the end of

the rst channel’s start-up time, the second channel start-

up is delayed. The second channel will then start 100ms

after the rst channel’s start-up timer has expired and the

TIMER pin, if used, reaches its 200mV low threshold.

When an external TIMER capacitor is used, the TIMER

capacitor voltage ramps up with a 100μA current. Once the

TIMER pin reaches its 1.235V threshold the TIMER begins

to discharge. While the TIMER capacitor is discharging, the

ON signal for the second channel should not be asserted

for 2ms/μF of TIMER capacitance. This allows the TIMER

capacitor to return to its low state and ensures that the next

channel to start receives a full timer cycle. This wait time

is unnecessary when using the internal 100ms timer.

Board Present Change of State

The EN pins may be used to detect the presence of one or

two downstream cards. Whenever an EN pin toggles, FAULT

bit 4 is set to indicate a change of state. When the EN pin

goes high, indicating board removal, the corresponding

GATE turns off immediately (with a 1mA current to ground)

and the board present STATUS bit 4, is cleared. If the EN

pin is pulled low, indicating a board insertion, all fault bits

for that channel except FAULT bit 4 are cleared and enable

STATUS bit 4, is set. If the EN pin remains low for 100ms

the state of the ON pin is captured in ‘FET On’ CONTROL

bit 3. This turns the switch on if the ON pin is tied high.

There is an internal 10μA pull-up current source on the

EN pin. If the CONFIG pin is tied low, both EN pins must

be low for 100ms for the two channels to be enabled and

if either EN pin goes high both channels will turn off.

If a channel shuts down due to a fault, it may be desirable

to restart that channel simply by removing and reinserting

the related load card. In cases where the LTC4222 and the

switch reside on a backplane or midplane and the load

resides on a plug-in card, the EN pin detects when the

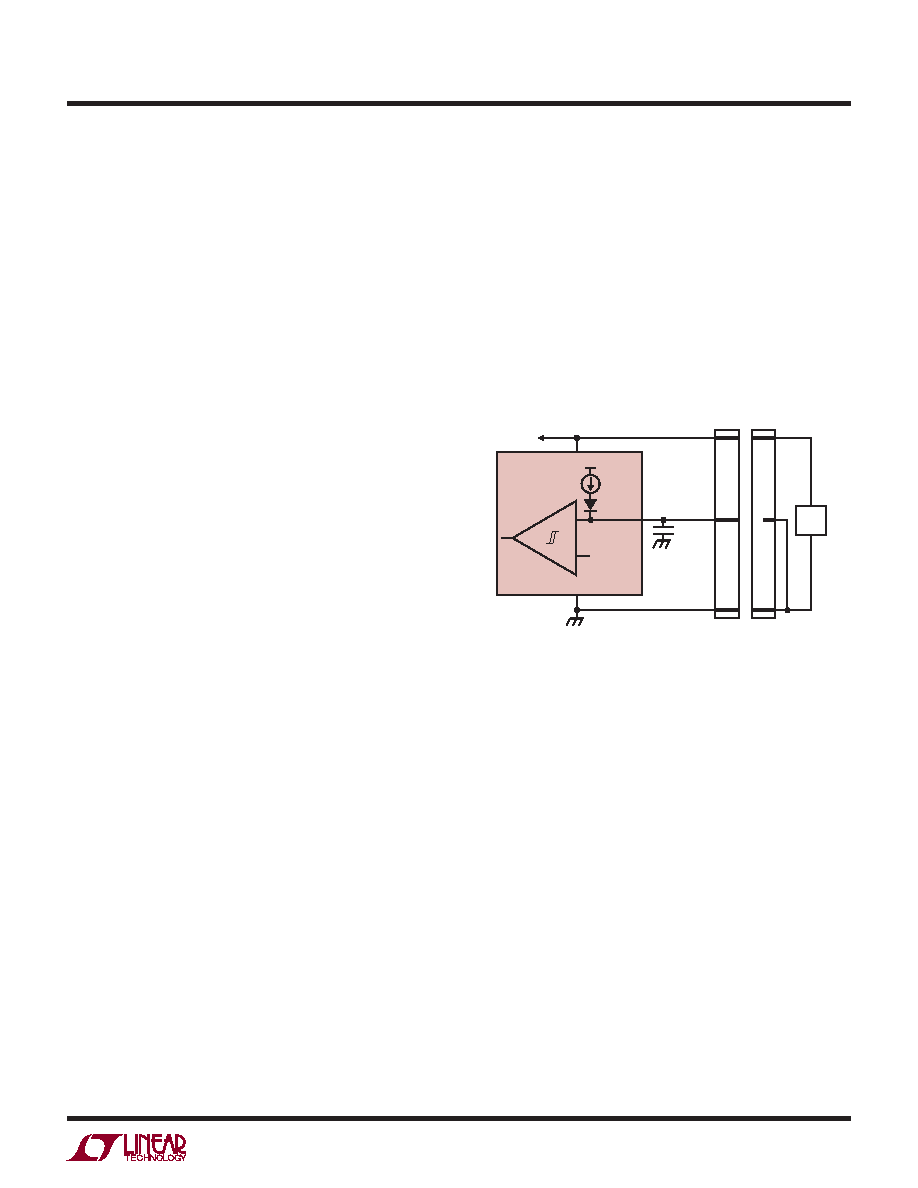

plug-in card is removed. Figure 4 shows an example where

the EN pin is used to detect insertion. Once the plug-in card

is reinserted the fault register is cleared except for FAULT

bit 4. After 100ms the state of the ON pin is latched into

bit 3 of the CONTROL register. At this point the channel

starts up again.

If a connection sense on the plug-in card is driving an EN

pin, insertion or removal of the card may cause the pin

voltage to bounce. This results in clearing the fault register

when the card is removed. The pin may be debounced

using a lter capacitor, CEN, on the EN pin as shown in

Figure 4. The lter time is given by:

tFILTER = CEN 123 (ms/μF)

Figure 4. Plug-In Card Insertion/Removal

–

+

1.235V

GND

MOTHERBOARD

CONNECTOR

PLUG-IN

CARD

SOURCE

OUT

LTC4222

10μA

EN

CEN

LOAD

4222 F04

FET Short Fault

A FET short fault is reported if the data converter measures

a current sense voltage greater than or equal to 2mV while

the corresponding GATE is turned off. This condition sets

FET short bit, Fault bit 5.

Power-Bad Fault

A power-bad fault is reported if a FB pin voltage drops

below its 1.235V threshold for more than 2μs when the

corresponding GATE is above the 4.3V gate to source

threshold. This pulls the GPIO pin low immediately in the

default power good conguration, and sets power-bad

present bit, STATUS bit 3, and power-bad bit, FAULT bit 3.

A circuit prevents power-bad faults if the GATE-to-SOURCE

voltage is low, eliminating false power-bad faults during

power-up or power-down. If the FB pin voltage subsequently

rises back above the threshold, a power good congured

GPIO pin returns to a high impedance state and STATUS

bit 3 is reset.

相关PDF资料 |

PDF描述 |

|---|---|

| LSN-1.3/10-D12J | DC-DC REG PWR SUPPLY MODULE |

| LSN-1.8/10-D12J | DC-DC REG PWR SUPPLY MODULE |

| LSN-2/10-D12J | DC-DC REG PWR SUPPLY MODULE |

| LSN-5/10-D12 | DC-DC REG PWR SUPPLY MODULE |

| LM4040DIM-10.0X | 1-OUTPUT TWO TERM VOLTAGE REFERENCE, 10 V, PDSO8 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LTC4222IG#PBF | 功能描述:IC CTRLR DUAL HOT SWAP 36-SSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 热交换 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:119 系列:- 类型:热交换控制器 应用:通用型,PCI Express? 内部开关:无 电流限制:- 电源电压:3.3V,12V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:80-TQFP 供应商设备封装:80-TQFP(12x12) 包装:托盘 产品目录页面:1423 (CN2011-ZH PDF) |

| LTC4222IG#TRPBF | 功能描述:IC CTRLR DUAL HOT SWAP 36-SSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 热交换 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:119 系列:- 类型:热交换控制器 应用:通用型,PCI Express? 内部开关:无 电流限制:- 电源电压:3.3V,12V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:80-TQFP 供应商设备封装:80-TQFP(12x12) 包装:托盘 产品目录页面:1423 (CN2011-ZH PDF) |

| LTC4222IG-PBF | 制造商:LINER 制造商全称:Linear Technology 功能描述:Dual Hot Swap Controller with I2C Compatible Monitoring |

| LTC4222IG-TRPBF | 制造商:LINER 制造商全称:Linear Technology 功能描述:Dual Hot Swap Controller with I2C Compatible Monitoring |

| LTC4222IUH#PBF | 功能描述:IC CTRLR DUAL HOT SWAP 32-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 热交换 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:119 系列:- 类型:热交换控制器 应用:通用型,PCI Express? 内部开关:无 电流限制:- 电源电压:3.3V,12V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:80-TQFP 供应商设备封装:80-TQFP(12x12) 包装:托盘 产品目录页面:1423 (CN2011-ZH PDF) |

发布紧急采购,3分钟左右您将得到回复。