- 您现在的位置:买卖IC网 > PDF目录369885 > LXT3108BE LINE INTERFACE|BGA|256PIN|PLASTIC PDF资料下载

参数资料

| 型号: | LXT3108BE |

| 英文描述: | LINE INTERFACE|BGA|256PIN|PLASTIC |

| 中文描述: | 线路接口|的BGA | 256PIN |塑料 |

| 文件页数: | 23/26页 |

| 文件大小: | 402K |

| 代理商: | LXT3108BE |

T1 CSU/ISDN PRI Transceiver

—

LXT310

Datasheet

23

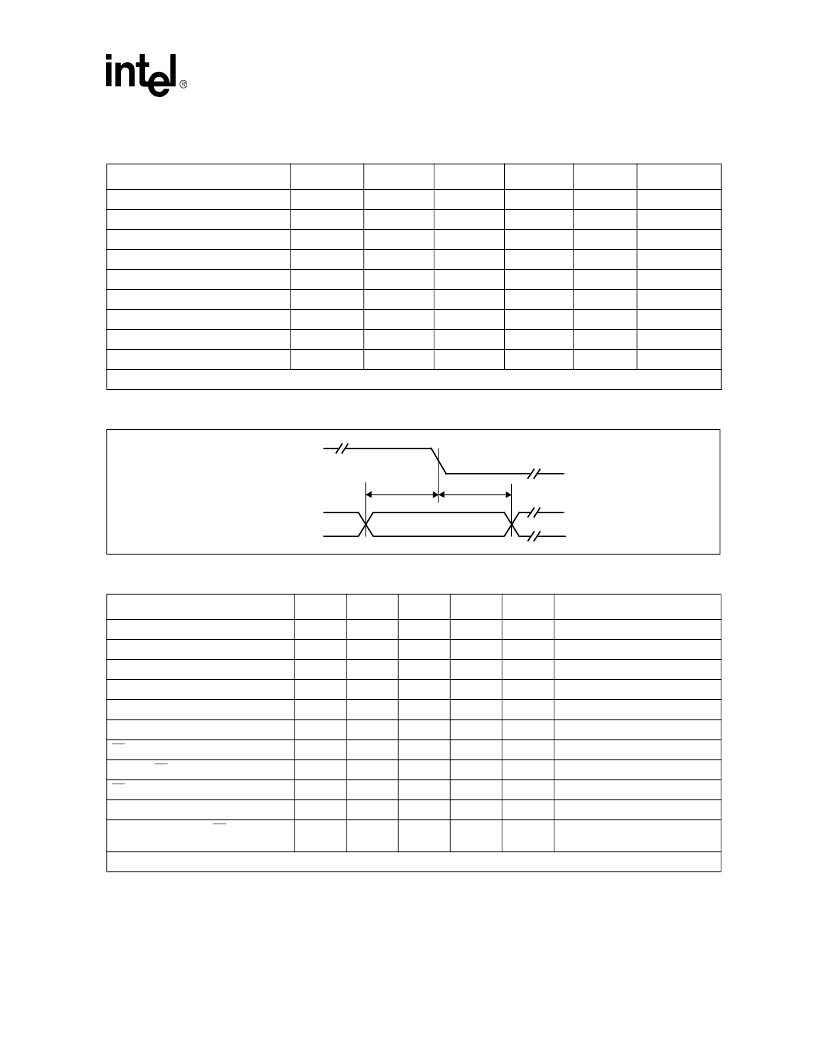

Table 13. LXT310 Master Clock and Transmit Timing Characteristics

(See

Figure 11

)

Parameter

Sym

Min

Typ

1

Max

Units

Notes

Master clock frequency

MCLK

–

1.544

–

MHz

Master clock tolerance

MCLKt

–

±100

–

ppm

Master clock duty cycle

MCLKd

40

–

60

%

Crystal frequency

fc

–

6.176

–

MHz

LXT310 only

Transmit clock frequency

TCLK

–

1.544

–

MHz

Transmit clock tolerance

TCLKt

–

–

±100

ppm

Transmit clock duty cycle

TCLKd

10

–

90

%

TPOS/TNEG to TCLK setup time

t

SUT

50

–

–

ns

TCLK to TPOS/TNEG hold time

t

HT

50

–

–

ns

1. Typical values are at 25

°

C and are for design aid only; they are not guaranteed and not subject to production testing.

Figure 11. LXT310 Transmit Clock Timing Diagram

Table 14. LXT310 Serial I/O Timing Characteristics

(See

Figure 12

and

Figure 13

)

Parameter

Sym

Min

Typ

1

Max

Units

Test Conditions

Rise/Fall time - any digital output

t

RF

–

–

100

ns

Load 1.6 mA, 50 pF

SDI to SCLK setup time

t

DC

50

–

–

ns

SCLK to SDI hold time

t

CDH

50

–

–

ns

SCLK low time

t

CL

240

–

–

ns

SCLK high time

t

CH

240

–

–

ns

SCLK rise and fall time

t

R

, t

F

–

–

50

ns

CS

to SCLK setup time

t

CC

50

–

–

ns

SCLK to

CS

hold time

t

CCH

50

–

–

ns

CS

inactive time

t

CWH

250

–

–

ns

SCLK to SDO valid

t

CDV

–

–

200

ns

SCLK falling edge or

CS

rising edge

to SDO high Z

t

CDZ

–

100

–

ns

1. Typical values are at 25

°

C and are for design aid only; they are not guaranteed and not subject to production testing.

t

HT

t

SUT

TCLK

TPOS

TNEG

相关PDF资料 |

PDF描述 |

|---|---|

| LXT3108HE | LINE INTERFACE|QFP|208PIN|PLASTIC |

| LXT310JE | PCM Transceiver |

| LXT310NE | PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|DIP|28PIN|PLASTIC |

| LXT316NE | PCM Repeater |

| LXT316PE | PCM Repeater |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LXT3108HE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:LINE INTERFACE|QFP|208PIN|PLASTIC |

| LXT310JE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:PCM Transceiver |

| LXT310NE | 制造商:LEVEL ONE 功能描述: |

| LXT310PE | 制造商:Intel 功能描述: 制造商:LEVEL_ONE 功能描述: 制造商:LEVEL ONE 功能描述:PCM TRANSCEIVER, Single, T-1(DS1), 28 Pin, Plastic, PLCC |

| LXT310PE-IJC8 | 制造商:LEVE ONE 功能描述:310PE-IJC8 |

发布紧急采购,3分钟左右您将得到回复。