- 您现在的位置:买卖IC网 > PDF目录80354 > M32170F4VWG 32-BIT, FLASH, 40 MHz, RISC MICROCONTROLLER, PBGA255 PDF资料下载

参数资料

| 型号: | M32170F4VWG |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, FLASH, 40 MHz, RISC MICROCONTROLLER, PBGA255 |

| 封装: | 17 X 17 MM, FBGA-255 |

| 文件页数: | 20/49页 |

| 文件大小: | 561K |

| 代理商: | M32170F4VWG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页

Mitsubishi Microcomputers

27

SINGLE-CHIP 32-BIT CMOS MICROCOMPUTER

2001-5-14 Rev.1.0

32170 Group, 32174 Group

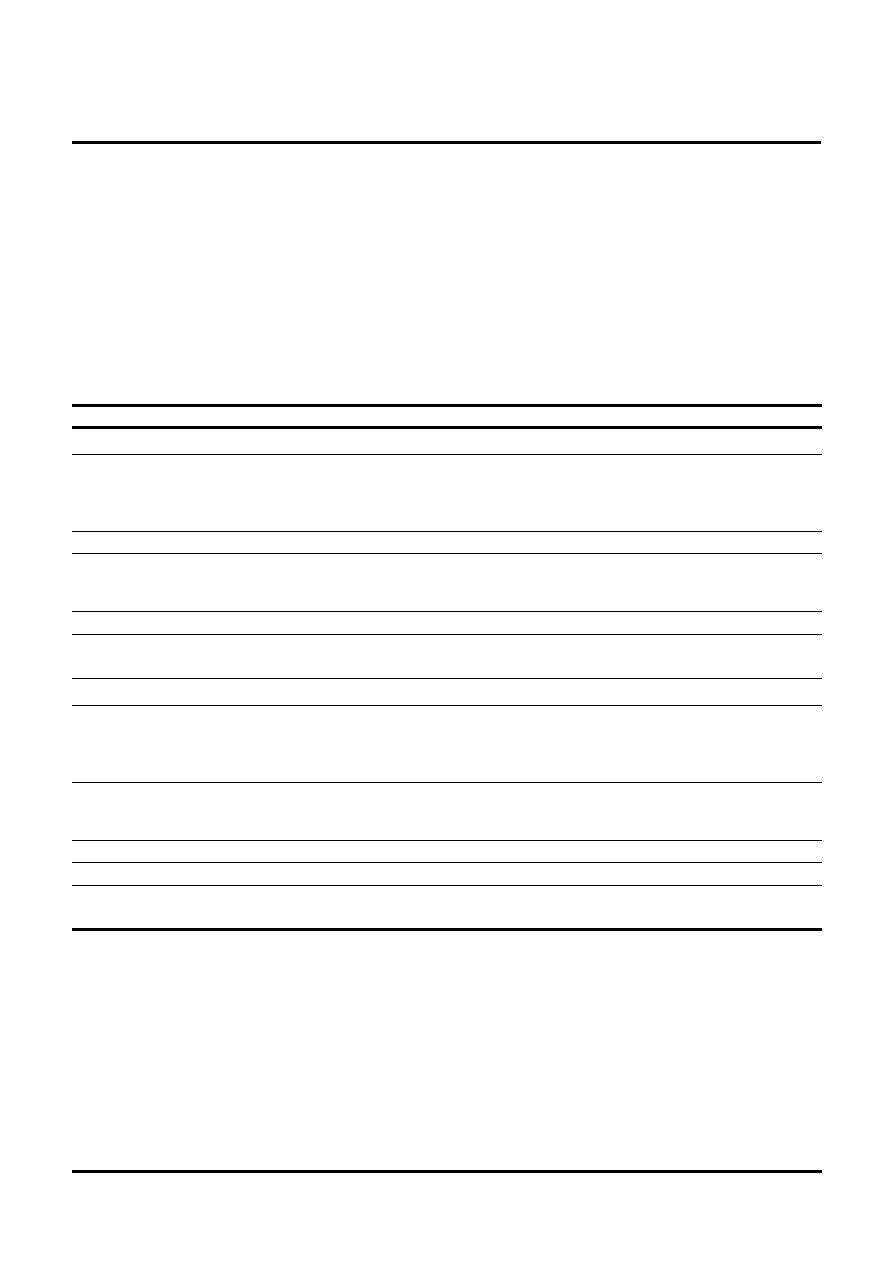

Item

Content

Number of channels

10 channels

Transfer request

Software trigger

Request from internal peripheral I/O: A-D converter, multijunction timer, or serial I/O

(reception completed, transmit buffer empty)

Cascaded connection between DMA channels possible (Note)

Maximum number of times transferred

256 times

Transferable address space

64 Kbytes (address space from H’0080 0000 to H’0080 FFFF)

Transfers between internal peripheral I/Os, between internal RAM and internal peripheral IO,

and between internal RAMs are supported

Transfer data size

16 bits or 8 bits

Transfer method

Single transfer DMA (control of the internal bus is relinquished for each transfer performed),

dual-address transfer

Transfer mode

Single transfer mode

Direction of transfer

One of three modes can be selected for the source and destination of transfer:

Address fixed

Address increment

32-channel ring buffer

Channel priority

Channel 0 > channel 1 > channel 2 > channel 3 > channel 4 >

channel 5 > channel 6 > channel 7 > channel 8 > channel 9

(Fixed priority)

Maximum transfer rate

13.3 Mbytes per second (when internal peripheral clock = 20 MHz)

Interrupt request

Group interrupt request can be generated when each transfer count register underflows

Transfer area

64 Kbytes from H’0080 0000 to H’0080 FFFF (Transfer is possible in the entire internal

RAM/SFR area)

Note: The following DMA channels can be cascaded.

DMA transfer on channel 1 started at end of one DMA transfer on channel 0

DMA transfer on channel 2 started at end of one DMA transfer on channel 1

DMA transfer on channel 0 started at end of one DMA transfer on channel 2

DMA transfer on channel 4 started at end of one DMA transfer on channel 3

DMA transfer on channel 6 started at end of one DMA transfer on channel 5

DMA transfer on channel 7 started at end of one DMA transfer on channel 6

DMA transfer on channel 5 started at end of one DMA transfer on channel 7

DMA transfer on channel 9 started at end of one DMA transfer on channel 8

DMA transfer on channel 5 started at end of all DMA transfers on channel 0 (underflow of transfer count register)

Built-in 10-Channel DMAC

The microcomputer contains 10 channels of DMAC, allowing

for data transfer between internal peripheral I/Os, between

internal RAM and internal peripheral I/O, and between inter-

nal RAMs.

DMA transfer requests can be issued from the user-cre

ated software, as well as can be triggered by a signal gener-

ated by the internal peripheral I/O (A-D converter, MJT, or

serial I/O).

Table 16 Outline of the DMAC

The microcomputer also supports cascaded connection be-

tween DMA channels (starting DMA transfer on a channel at

end of transfer on another channel). This makes advanced

transfer processing possible without causing any additional

CPU load.

相关PDF资料 |

PDF描述 |

|---|---|

| MB90423GBPF | 16-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP100 |

| MB90427GCPF | 16-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP100 |

| MB90F423GCPF | 16-BIT, FLASH, 16 MHz, MICROCONTROLLER, PQFP100 |

| M30280MC-XXXHP-U3 | 16-BIT, MROM, 20 MHz, MICROCONTROLLER, PQFP80 |

| MC3S12Q32CFA8 | 16-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M32170F6VFP | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 32-BIT CMOS MICROCOMPUTER |

| M32170F6VWG | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 32-BIT CMOS MICROCOMPUTER |

| M32170T-PTC | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:Converter for In-circuit Connection (for 32170, 32174 Group) |

| M32171F2VFP | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 32-BIT CMOS MICROCOMPUTER |

| M32171F3VFP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:32-BIT RISC SINGLE-CHIP MICROCOMPUTER M32R FAMILY / M32R/ECU SERIES |

发布紧急采购,3分钟左右您将得到回复。