- 您现在的位置:买卖IC网 > PDF目录67761 > M34283G2GP 4-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO20 PDF资料下载

参数资料

| 型号: | M34283G2GP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 4-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO20 |

| 封装: | 4.40 X 6.50 MM, 0.65 MM PITCH, PLASTIC, LSSOP-20 |

| 文件页数: | 2/41页 |

| 文件大小: | 441K |

| 代理商: | M34283G2GP |

第1页当前第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页

Rev.1.01

Mar 20, 2006

page 8 of 62

REJ03B0109-0101

4283 Group

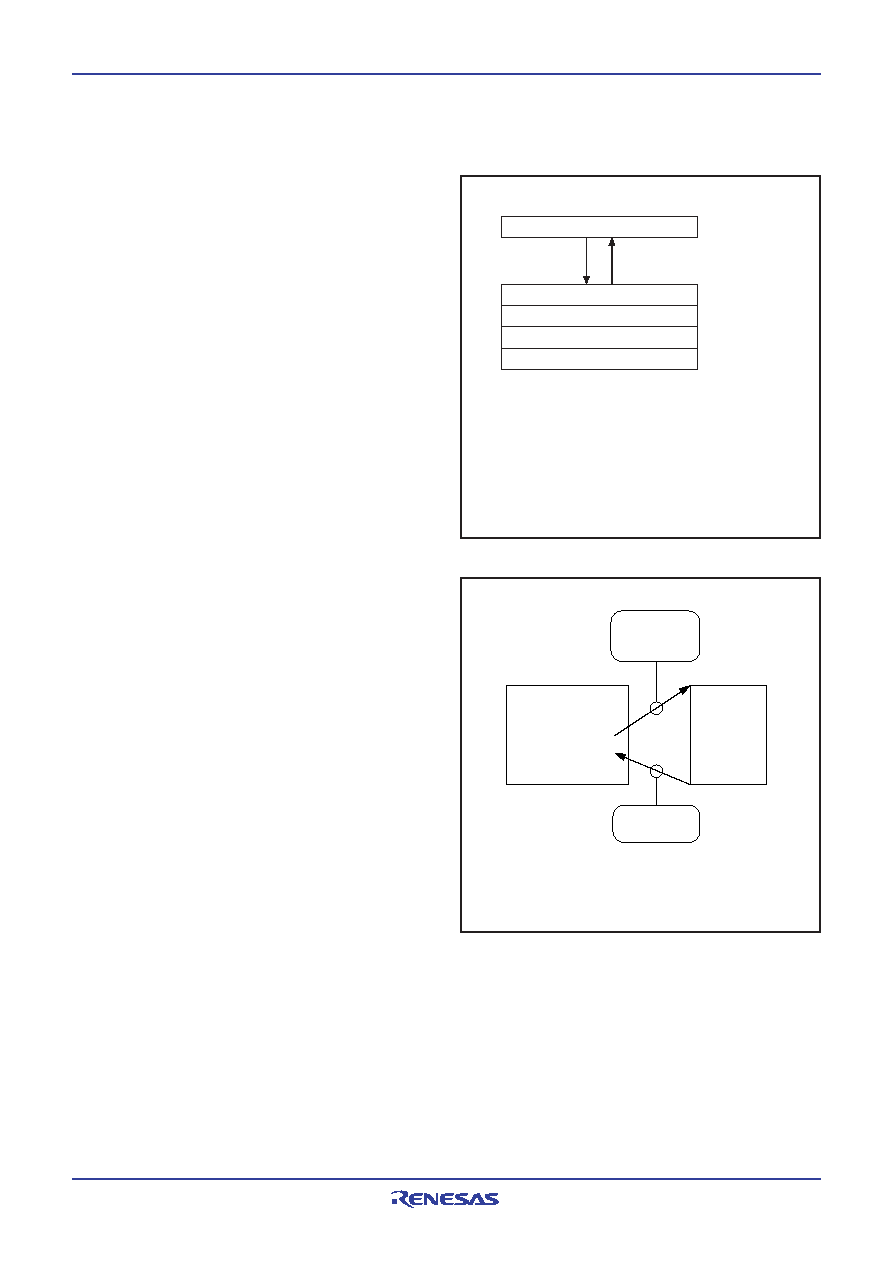

Fig. 5 Stack registers (SKs) structure

Fig. 6 Example of operation at subroutine call

(5) Most significant ROM code reference enable flag (URS)

URS flag controls whether to refer to the contents of the most

significant 1 bit (bit 8) of ROM code when executing the TABP

p instruction. If URS flag is “0,” the contents of the most

significant 1 bit of ROM code is not referred even when

executing the TABP p instruction. However, if URS flag is “1,”

the contents of the most significant 1 bit of ROM code is set to

flag CY when executing the TABP p instruction (Figure 4).

URS flag is “0” after system is released from reset and returned

from RAM back-up mode. It can be set to “1” with the URSC

instruction, but cannot be cleared to “0.”

(6) Stack registers (SKs) and stack pointer (SP)

Stack registers (SKs) are used to temporarily store the contents

of program counter (PC) just before branching until returning

to the original routine when;

performing a subroutine call, or

executing the table reference instruction (TABP p).

Stack registers (SKs) are four identical registers, so that

subroutines can be nested up to 4 levels. However, one of

stack registers is used when executing a table reference

instruction. Accordingly, be careful not to over the stack. The

contents of registers SKs are destroyed when 4 levels are

exceeded.

The register SK nesting level is pointed automatically by 2-bit

stack pointer (SP).

Figure 5 shows the stack registers (SKs) structure.

Figure 6 shows the example of operation at subroutine call.

(7) Skip flag

Skip flag controls skip decision for the conditional skip

instructions and continuous described skip instructions.

Note : The 4283 Group just invalidates the next instruction

when a skip is performed. The contents of program

counter is not increased by 2. Accordingly, the number

of cycles does not change even if skip is not performed.

However, the cycle count becomes “1” if the TABP p,

RT, or RTS instruction is skipped.

SK0

SK1

SK2

SK3

(SP) = 0

(SP) = 1

(SP) = 2

(SP) = 3

Program counter (PC)

Executing RT

instruction

Executing BM

instruction

Stack pointer (SP) points “3” at reset or

returning from RAM back-up mode. It points “0”

by executing the first BM instruction, and the

contents of program counter is stored in SK0.

When the BM instruction is executed after four

stack registers are used ((SP) = 3), (SP) = 0

and the contents of SK0 is destroyed.

Returning to the BM instruction execution

address with the RT instruction, and the BM

instruction is equivalent to the NOP instruction.

(SP)

← 0

(SK0)

← 000116

(PC)

← SUB1

Main program

000216 NOP

Address

000016 NOP

000116 BM SUB1

Subroutine

SUB1 :

NOP

RT

(PC)

← (SK0)

(SP)

← 3

Note:

相关PDF资料 |

PDF描述 |

|---|---|

| M34283G2-XXXGP | 4-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO20 |

| M34502E4FP | 4-BIT, OTPROM, MICROCONTROLLER, PDSO24 |

| M34502M4-XXXFP | 4-BIT, MROM, MICROCONTROLLER, PDSO24 |

| M34502M2-XXXFP | 4-BIT, MROM, MICROCONTROLLER, PDSO24 |

| M34508G4GP | 4-BIT, MROM, 6 MHz, MICROCONTROLLER, PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M34283G2GP#U1 | 制造商:Renesas Electronics Corporation 功能描述:MICROCONTROLLER |

| M34283G2-XXXGP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34286 | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34286G2GP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34286G2GP#U0 | 功能描述:MCU 1.8/3.6V 2KB ROM 20-LSSOP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微控制器, 系列:720/4500 标准包装:38 系列:Encore!® XP® 核心处理器:eZ8 芯体尺寸:8-位 速度:5MHz 连通性:IrDA,UART/USART 外围设备:欠压检测/复位,LED,POR,PWM,WDT 输入/输出数:16 程序存储器容量:4KB(4K x 8) 程序存储器类型:闪存 EEPROM 大小:- RAM 容量:1K x 8 电压 - 电源 (Vcc/Vdd):2.7 V ~ 3.6 V 数据转换器:- 振荡器型:内部 工作温度:-40°C ~ 105°C 封装/外壳:20-SOIC(0.295",7.50mm 宽) 包装:管件 其它名称:269-4116Z8F0413SH005EG-ND |

发布紧急采购,3分钟左右您将得到回复。