- 您现在的位置:买卖IC网 > PDF目录69011 > M35049-001FP 24 X 12 CHARACTERS CRT CHAR DSPL CTLR, PDSO20 PDF资料下载

参数资料

| 型号: | M35049-001FP |

| 元件分类: | 显示控制器 |

| 英文描述: | 24 X 12 CHARACTERS CRT CHAR DSPL CTLR, PDSO20 |

| 封装: | 0.300 INCH, PLASTIC, SSOP-20 |

| 文件页数: | 35/39页 |

| 文件大小: | 439K |

| 代理商: | M35049-001FP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页当前第35页第36页第37页第38页第39页

MITSUBISHI MICROCOMPUTERS

M35049-XXXFP

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

4

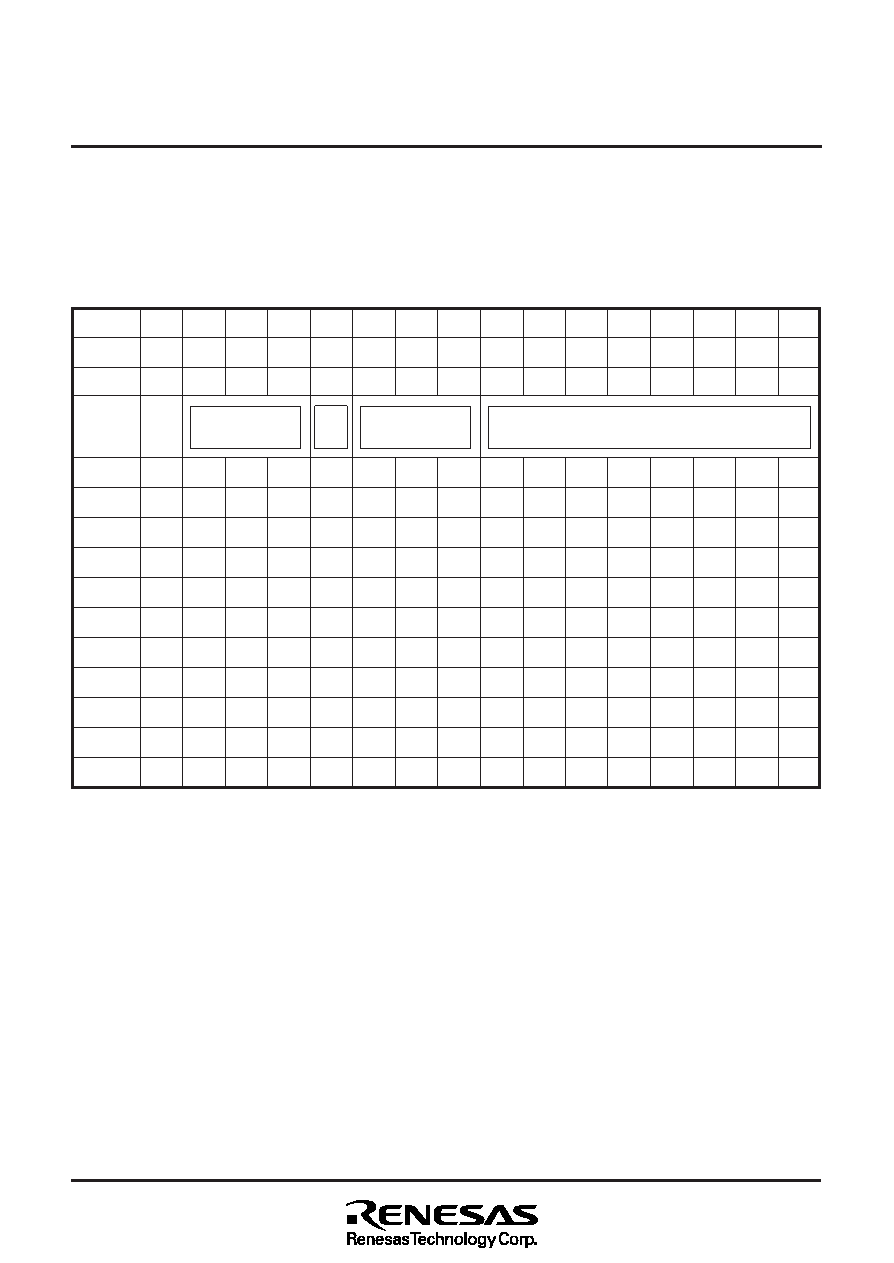

MEMORY CONSTITUTION

Address 00016 to 11F16 are assigned to the display RAM, address

12016 to 12816 are assigned to the display control registers. The

internal circuit is reset and all display control registers (address

__

12016 to 12816) are set to “0” when the AC pin level is “L”. And

then, RAM is not erased and be undefinited. This memory is con-

Fig. 1 Memory constitution (page 0 memory)

sisted of 2 pages : page 0 memory and page 1 memory (their ad-

dresses are common), page controlled by DAF bit of each address

when writing data. For detail, see “DATA INPUT EXAMPLE”.

Memory constitution is shown in Figure 1 and 2.

………

DAF

DAE

DAD

DAC

DAB

DAA

DA9

DA8

DA7

DA6

DA5

DA4

DA3

DA2

DA1

DA0

0

BB

BG

BR

BLINK

B

G

R

C7

C6

C5

C4

C3

C2

C1

C0

0

BB

BG

BR

BLINK

B

G

R

C7

C6

C5

C4

C3

C2

C1

C0

0

BB

BG

BR

BLINK

B

G

R

C7

C6

C5

C4

C3

C2

C1

C0

0

BB

BG

BR

BLINK

B

G

R

C7

C6

C5

C4

C3

C2

C1

C0

0

TEST27 VJT

TEST26 TEST25 TEST24 TEST23 TEST22 TEST21 TEST20 TEST19 TEST18 TEST17 TEST16 TEST15 TEST14

0

TEST28 PTD7

PTD6

PTD5

PTD4

PTD3

PTD2

PTD1

PTD0

PTC5

PTC4

PTC3

PTC2

PTC1

PTC0

0

TEST31SPACE2 SPACE1 SPACE0 TEST30 TEST29 HP8

HP7

HP6

HP5

HP4

HP3

HP2

HP1

HP0

0

TEST34 TEST3 TEST2 TEST1 TEST0 TEST33 TEST32

VP7

VP6

VP5

VP4

VP3

VP2

VP1

VP0

0

TEST9 TEST5 TEST4 DSP11 DSP10 DSP9

DSP8

DSP7

DSP6

DSP5

DSP4

DSP3

DSP2

DSP1

DSP0

0

TEST10 VSZ1H1 VSZ1H0 VSZ1L1 VSZ1L0 V1SZ1 V1SZ0

LIN9

LIN8

LIN7

LIN6

LIN5

LIN4

LIN3

LIN2

0

POPUP VSZ2H1 VSZ2H0 VSZ2L1 VSZ2L0 V18SZ1 V18SZ0 LIN17 LIN16 LIN15 LIN14 LIN13 LIN12 LIN11 LIN10

0

MODE0 TEST12 HSZ20 TEST11 HSZ10 BETA14 TEST8 TEST7 TEST6

FB

FG

FR

RB

RG

RR

0

MODE1 BLINK2 BLINK1 BLINK0 DSPON TEST35 RAMERS SYAD

BLK1

BLK0

POLH POLV VMASK

__

B/F

BCOL

00016

00116

11E16

11F16

12016

12116

12216

12316

12416

12516

12616

12716

12816

Addresses

Background

coloring

Blink-

ing

Character color

Character code

相关PDF资料 |

PDF描述 |

|---|---|

| M35051-001SP | 24 X 10 CHARACTERS CRT CHAR DSPL CTLR, PDIP20 |

| M35052-001FP | 24 X 10 CHARACTERS CRT CHAR DSPL CTLR, PDSO20 |

| M35052-XXXFP | 24 X 10 CHARACTERS CRT CHAR DSPL CTLR, PDSO20 |

| M35054-001FP | 24 X 10 CHARACTERS CRT CHAR DSPL CTLR, PDSO20 |

| M35055-001FP | 24 X 10 CHARACTERS CRT CHAR DSPL CTLR, PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M35049-XXXFP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS |

| M3505002 | 制造商:Delfingen 功能描述:300 ft??Conduit Convolute 9MM |

| M3505002-C | 制造商:Delfingen 功能描述:CDT CNVLT 9MM |

| M3505002-L | 制造商:Delfingen 功能描述: |

| M3505003 | 制造商:Delfingen 功能描述:CDT CNVLT 10MM |

发布紧急采购,3分钟左右您将得到回复。