- 您现在的位置:买卖IC网 > PDF目录67763 > M37733S4BFP 16-BIT, 25 MHz, MICROCONTROLLER, PQFP80 PDF资料下载

参数资料

| 型号: | M37733S4BFP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 16-BIT, 25 MHz, MICROCONTROLLER, PQFP80 |

| 封装: | 14 X 20 MM, 0.80 MM PITCH, PLASTIC, QFP-80 |

| 文件页数: | 8/39页 |

| 文件大小: | 826K |

| 代理商: | M37733S4BFP |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页

13

MITSUBISHI MICROCOMPUTERS

M37733S4BFP

16-BIT CMOS MICROCOMPUTER

New

product

____

HLDA

is a hold acknowledge signal and is used to notify externally

____

when the microcomputer receives HOLD input and enters hold state.

____

HOLD

is a hold request signal. It is an input signal used to put the

____

microcomputer in hold state. HOLD input is accepted when the internal

clock

falls from “H” level to “L” level while the bus is not used.

P00/A0 to P07/A7 pins, P10/A8/D8 to P17/A15/D15 pins, P20/A16/D0 to

_

___

P27/A23/D7 pins, P30/R/W pin, and P31/BHE pin are floating while the

microcomputer stays in hold state. These pins are floating after one

____

cycle of the internal clock

later than HLDA signal changes to “L”

level. At the removing of hold state, these ports are removed from

____

floating state after one cycle of internal clock

later than HLDA signal

changes to “H” level.

___

RDY

is a ready signal. If this signal goes “L”, the internal clock

___

stops at “L”. RDY is used when slow external memory is attached.

P42/

1

pin is an output pin for clock

1

. The

1

output is

___

independent of RDY and does not stop even when internal clock

___

stops because of “L” input to the RDY pin. As shown in Table 2,

1

output can also be stopped with the signal output disable selection

bit “1”. In this case, write “1” to the port P42 direction register.

(2) Evaluation chip mode [11]

Evaluation chip mode is entered by applying voltage twice the VCC

voltage to the CNVSS pin. This mode is normally used for evaluation

tools.

_

_ ___

____

The functions of E, P00/A0 to P07/A7 pins, R/W, BHE, ALE, and HLDA

are the same as those in microprocessor mode.

P10/A8/D8 to P17/A15/D15 pins function as address output pins while

__

E

is “H” and as data I/O pin of odd addresses while E is “L” regardless

of the BYTE pin level. However, if an internal memory is read, external

_

data is ignored while E is “L”. P20/A16/D0 to P27/A23/D7 pins function

_

as address output pins while E is “H” and as data I/O pin of even

_

addresses while E is “L” when the BYTE pin level is “L”. However, if

_

an internal memory is read, external data is ignored while E is “L”.

When the BYTE pin level is “H” or 2VCC, port P2 functions as an

_

address output pin while E is “H” and as data I/O pin of even and odd

_

addresses while E is “L”. However, if an internal memory is read,

_

external data is ignored while E is “L”.

Port P4 and its data direction which are located at address 0A16 and

0C16 are treated differently in evaluation chip mode. When these

addresses are accessed, the data bus width is treated as 16 bits

regardless of the BYTE pin level, and the access cycle is treated as

internal memory regardless of the wait bit.

____

___

The functions of HOLD and RDY are the same as those in

microprocessor mode. Clock

1

from P42/

1

pin is always output

regardless of signal output disable selection bit.

Ports P43 to P46 become MX, QCL, VDA, and VPA output pins

___

respectively. Port P47 becomes the DBC input pin.

The MX signal normally contents of flag m, but the contents of flag x

is output if the CPU is using flag x.

QCL is the queue buffer clear signal. It becomes “H” when the

instruction queue buffer is cleared, for example, when a jump

instruction is executed.

VDA is the valid data address signal. It becomes “H” while the CPU

is reading data from data buffer or writing data to data buffer. It also

becomes “H” when the first byte of the instruction (operation code) is

read from the instruction queue buffer.

VPA is the valid program address signal. It becomes “H” while the

CPU is reading an instruction code from the instruction queue buffer.

___

DBC

is the debug control signal and is used for debugging. Table 1

shows the relationship between the CNVSS pin input levels and

processor modes.

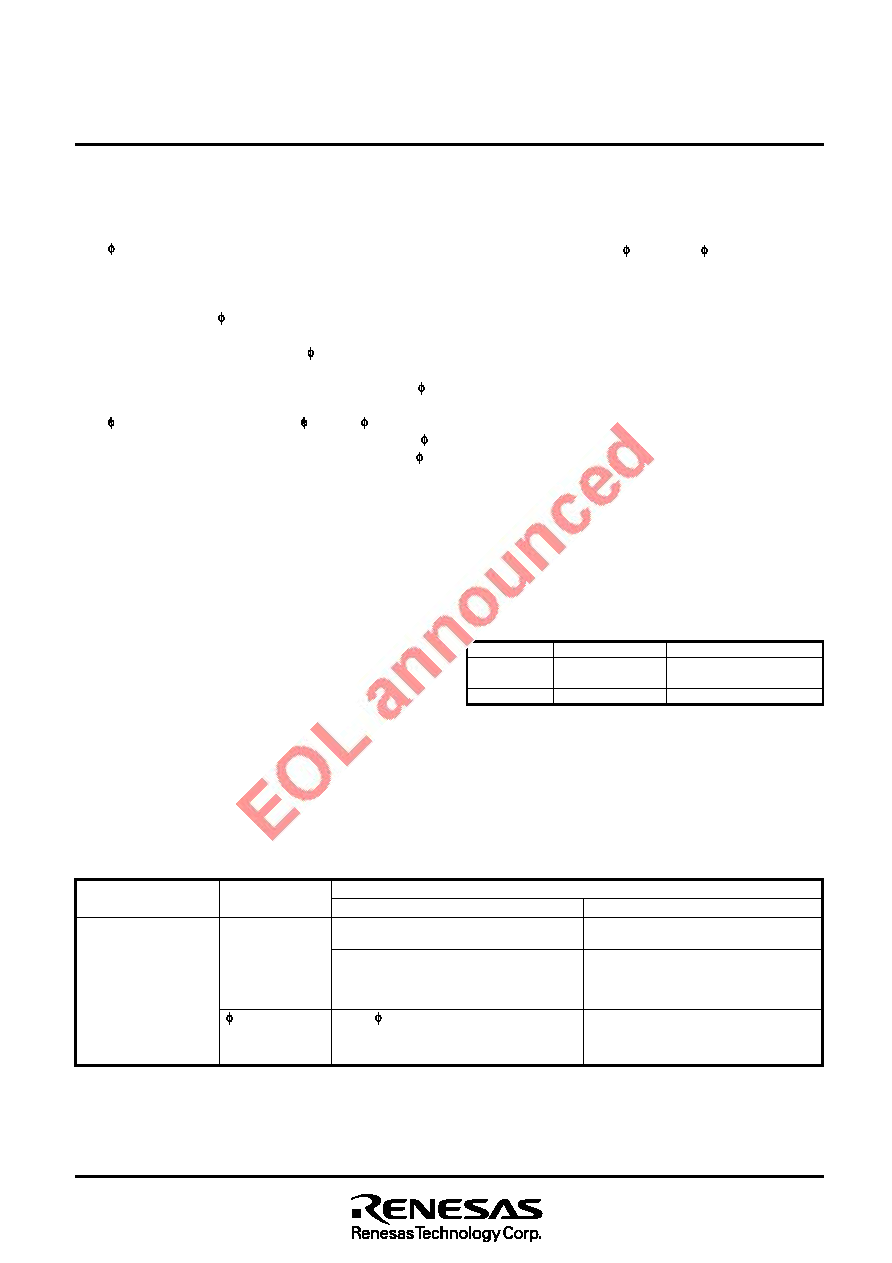

Table 1. Relationship between CNVss pin input levels and processor

modes

CNVss

Mode

Description

Microprocessor

( Evaluation chip)

Vss

Microprocessor mode upon

starting after reset.

2 Vcc

Evaluation chip

Evaluation chip mode only.

_

E

_

E

is output when the internal/external memory

_

E

is output only when the external memory

area is accessed.

After WIT/STP instruction is executed,

“L” is output after WIT/STP instruction is

“H” is output.

executed.

Microprocessor mode

Standby state selection bit (bit 0 of port

function control register) must be set to “1”.

1

Clock

1

is output.

“H”or “L” is output. (Output the content of

P42 latch.)

Port P42 direction register must be set to

“1”.

Table 2. Function of signal output disable selection bit CM6 (bit 6 of oscillation circuit control register 0)

Function

CM6 = “0”

CM6 = “1”

Processor mode

Pin

Note. Functions shown in Table 2 cannot be emulated in a debugger.

相关PDF资料 |

PDF描述 |

|---|---|

| M37735MHLXXXHP | 16-BIT, MROM, 12 MHz, MICROCONTROLLER, PQFP80 |

| M37753M6C-XXXHP | 16-BIT, MROM, 40 MHz, MICROCONTROLLER, PQFP80 |

| M37754FFCGP | 16-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQFP100 |

| M37905F8CFP | 16-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP64 |

| M37905F8CSP | 16-BIT, FLASH, 20 MHz, MICROCONTROLLER, PDIP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M37733S4LHP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:16-BIT CMOS MICROCOMPUTER |

| M37733TL-HPD | 制造商:Renesas Electronics Corporation 功能描述:DEV 7733 GROUP EMULATION POD - Bulk |

| M37735EHB | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:PROM VERSION OF M37735EHBXXXFP |

| M37735EHBFS | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:PROM VERSION OF M37735MHBXXXFP |

| M37735EHBXXXFP | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:PROM VERSION OF M37735EHBXXXFP |

发布紧急采购,3分钟左右您将得到回复。