- 您现在的位置:买卖IC网 > PDF目录383300 > M470L3224BT0 (SAMSUNG SEMICONDUCTOR CO. LTD.) 256MB DDR SDRAM MODULE PDF资料下载

参数资料

| 型号: | M470L3224BT0 |

| 厂商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 256MB DDR SDRAM MODULE |

| 中文描述: | 256MB的DDR内存模块 |

| 文件页数: | 13/20页 |

| 文件大小: | 264K |

| 代理商: | M470L3224BT0 |

DDR SDRAM

128MB, 256MB SODIMM Pb-Free

Revision 1.2 Oct. 2004

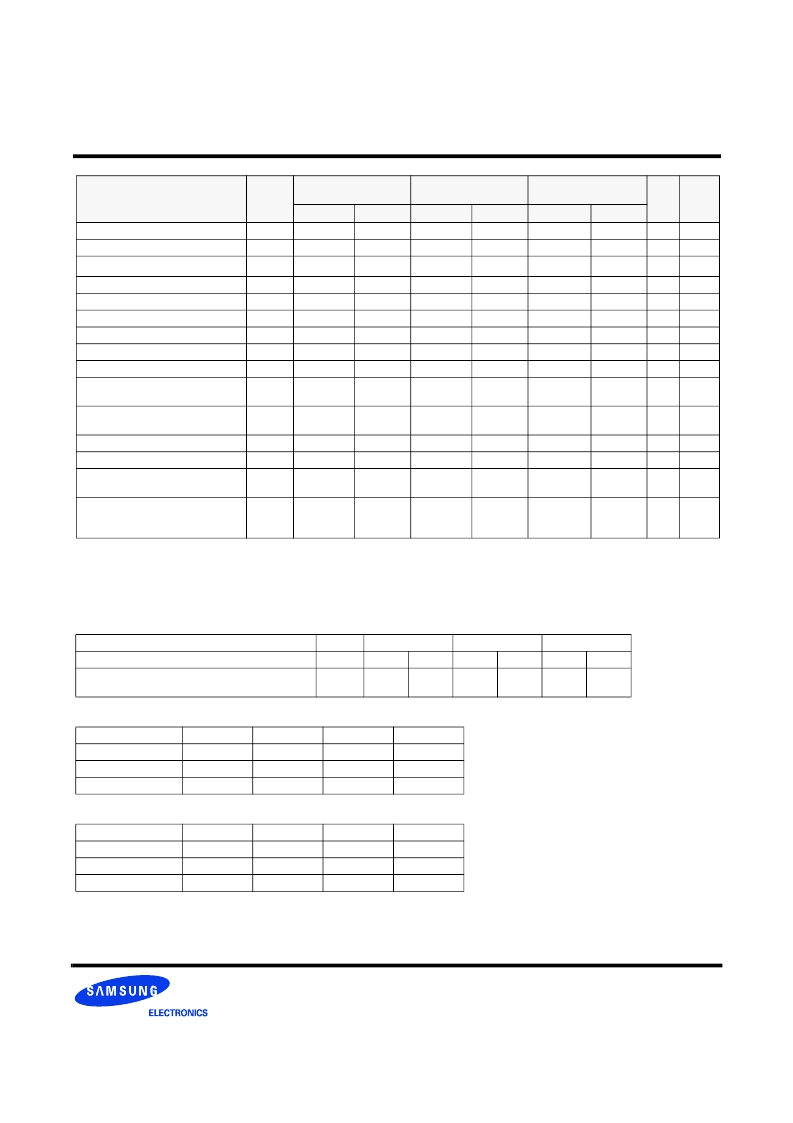

Parameter

Symbol

B3

(DDR333@CL=2.5))

Min

A2

(DDR266@CL=2.0)

Min

B0

(DDR266@CL=2.5))

Min

Unit

Note

Max

Max

Max

Mode register set cycle time

tMRD

12

15

15

ns

DQ & DM setup time to DQS

tDS

0.45

0.5

0.5

ns

j, k

DQ & DM hold time to DQS

tDH

0.45

0.5

0.5

ns

j, k

Control & Address input pulse width

tIPW

2.2

2.2

2.2

ns

8

DQ & DM input pulse width

tDIPW

1.75

1.75

1.75

ns

8

Power down exit time

tPDEX

6

7.5

7.5

ns

Exit self refresh to non-Read command

tXSNR

75

75

75

ns

Exit self refresh to read command

tXSRD

200

200

200

tCK

Refresh interval time

tREFI

7.8

7.8

7.8

us

4

Output DQS valid window

tQH

tHP

-tQHS

-

tHP

-tQHS

-

tHP

-tQHS

-

ns

11

Clock half period

tHP

tCLmin

or tCHmin

-

tCLmin

or tCHmin

-

tCLmin

or tCHmin

-

ns

10, 11

Data hold skew factor

tQHS

0.55

0.75

0.75

ns

11

DQS write postamble time

tWPST

0.4

0.6

0.4

0.6

0.4

0.6

tCK

2

Active to Read with Auto precharge

command

tRAP

18

20

20

Autoprecharge write recovery +

Precharge time

tDAL

(tWR/tCK)

+

(tRP/tCK)

(tWR/tCK)

+

(tRP/tCK)

(tWR/tCK)

+

(tRP/tCK)

tCK

13

System Characteristics for DDR SDRAM

The following specification parameters are required in systems using DDR333 & DDR266 devices to ensure proper sys-

tem performance. these characteristics are for system simulation purposes and are guaranteed by design.

Table 1 :

Input Slew Rate for DQ, DQS, and DM

Table 2

:

Input Setup & Hold Time Derating for Slew Rate

Table 3 : Input/Output Setup & Hold Time Derating for Slew Rate

AC CHARACTERISTICS

DDR333

DDR266

PARAMETER

SYMBOL

MIN

MAX

MIN

MAX

Units

Notes

DQ/DM/DQS input slew rate measured between

VIH(DC), VIL(DC) and VIL(DC), VIH(DC)

DCSLEW

TBD

TBD

TBD

TBD

V/ns

a, m

Input Slew Rate

tIS

tIH

Units

Notes

0.5 V/ns

0

0

ps

i

0.4 V/ns

+50

0

ps

i

0.3 V/ns

+100

0

ps

i

Input Slew Rate

tDS

tDH

Units

Notes

0.5 V/ns

0

0

ps

k

0.4 V/ns

+75

+75

ps

k

0.3 V/ns

+150

+150

ps

k

相关PDF资料 |

PDF描述 |

|---|---|

| M470L3224BTO | 256MB DDR SDRAM MODULE |

| M470L1624FU0-CA2 | DDR SDRAM SODIMM |

| M470L3224FU0-CA2 | Ring Core Bead Ferrite; Impedance:340ohm; Cable Diameter Max:0.203"; Width (Latch Included):1.23"; External Height:1.155"; External Width:1.125"; Length:1.25" |

| M485L1624FU0-CA2 | Ring Core Bead Ferrite; Impedance:200ohm; Cable Diameter Max:0.35"; Latch Height:0.2"; Width (Latch Included):0.885"; External Height:0.79"; External Width:0.77"; Length:1.45" |

| M470L1624FU0-CB0 | Split Core Ferrite Bead; Inner Diameter:0.45"; Package/Case:Split Ferrite Core; External Width:0.93"; Frequency:100MHz; Impedance:238ohm; Latch Height:0.38"; Mounting Type:Surface Mount; Width (Latch Included):1.035" RoHS Compliant: Yes |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M470L3224BTO | 制造商:SAMSUNG 制造商全称:Samsung semiconductor 功能描述:256MB DDR SDRAM MODULE |

| M470L3224DT0 | 制造商:SAMSUNG 制造商全称:Samsung semiconductor 功能描述:256MB DDR SDRAM MODULE |

| M470L3224DT0-CA0 | 制造商:SAMSUNG 制造商全称:Samsung semiconductor 功能描述:256MB DDR SDRAM MODULE |

| M470L3224DT0-CA2 | 制造商:SAMSUNG 制造商全称:Samsung semiconductor 功能描述:256MB DDR SDRAM MODULE |

| M470L3224DT0-CB0 | 制造商:SAMSUNG 制造商全称:Samsung semiconductor 功能描述:256MB DDR SDRAM MODULE |

发布紧急采购,3分钟左右您将得到回复。