- 您现在的位置:买卖IC网 > PDF目录383302 > M48T02-70PC1 (意法半导体) 16 Kbit 2Kb x8 TIMEKEEPER[ SRAM PDF资料下载

参数资料

| 型号: | M48T02-70PC1 |

| 厂商: | 意法半导体 |

| 英文描述: | 16 Kbit 2Kb x8 TIMEKEEPER[ SRAM |

| 中文描述: | 16千位2KB的x8计时器[静态存储器 |

| 文件页数: | 9/15页 |

| 文件大小: | 94K |

| 代理商: | M48T02-70PC1 |

DATA RETENTION MODE

WithvalidV

CC

applied,theM48T02/12operatesas

aconventionalBYTEWIDEstaticRAM.Shouldthe

supply voltage decay, the RAM will automatically

power-faildeselect,writeprotectingitselfwhenV

CC

falls within the V

PFD

(max), V

PFD

(min) window. All

outputsbecomehighimpedance,andallinputsare

treatedas ”don’t care.”

Note:

A power failure during a write cycle may

corrupt data at the currently addressed location,

but does not jeopardize the rest of the RAM’s

content.At voltagesbelowV

PFD

(min),the usercan

be assuredthe memorywill be in awrite protected

state,providedthe V

CC

falltime is not lessthan t

F

.

The M48T02/12 may respond to transient noise

spikeson V

CC

that reach into the deselectwindow

duringthe time thedevice is sampling V

CC

. There-

fore, decoupling of the power supply lines is rec-

ommended.

The power switching circuit connectsexternalV

CC

to the RAM and disconnectsthe batterywhen V

CC

rises above V

SO

. As V

CC

rises,the batteryvoltage

is checked. If the voltage is too low, an internal

BatteryNotOK(BOK) flagwillbe set.TheBOKflag

can be checkedafter power up. If the BOKflag is

set, the first write attempted will be blocked. The

flagisautomaticallyclearedafter thefirstwrite,and

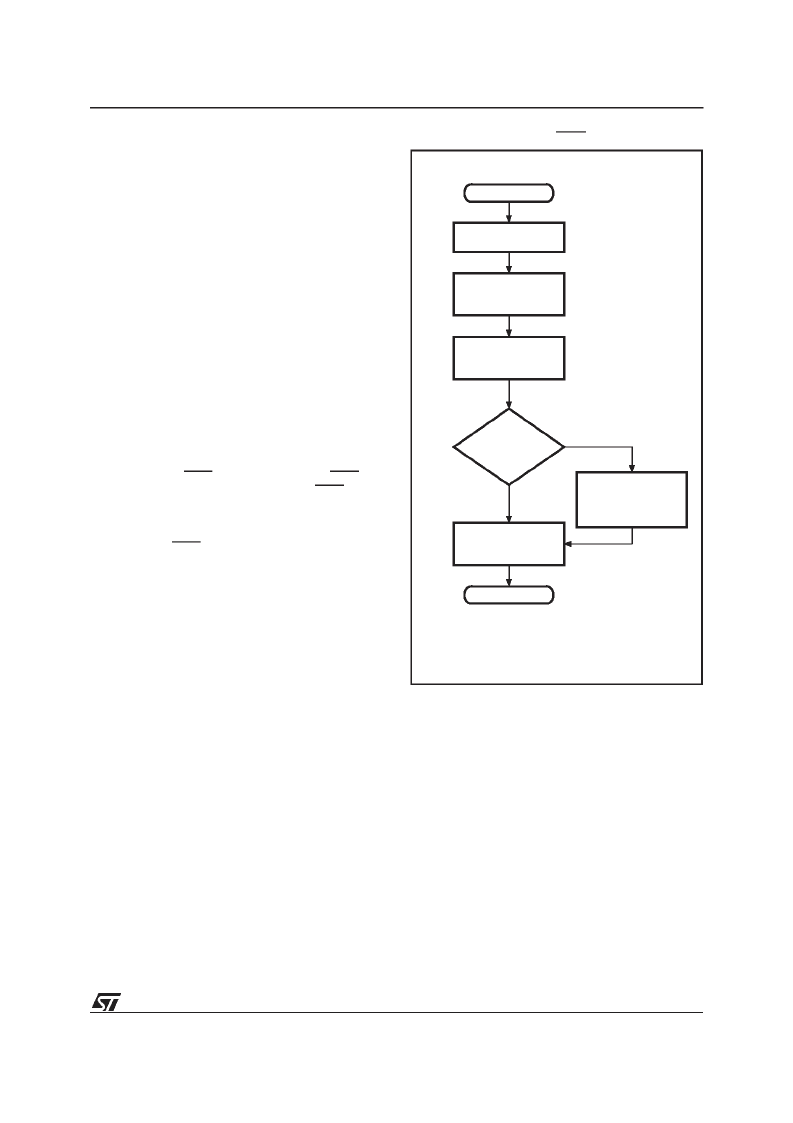

normal RAM operation resumes. Figure 9 illus-

trates how a BOK check routine could be struc-

tured.

For more information on a Battery Storage Life

referto the ApplicationNote AN1012.

CLOCKOPERATIONS

Reading the Clock

Updatesto the TIMEKEEPER registers should be

haltedbeforeclockdata is read to preventreading

data in transition. Because the BiPORT TIME-

KEEPER cells in the RAM array are only data

registers,andnot the actualclock counters,updat-

ing the registers can be halted without disturbing

the clock itself.

Updatingis haltedwhena ’1’iswrittento theREAD

bit, the seventh bit in the control register. As long

asa ’1’remains in thatposition,updatingis halted.

Afterahalt isissued,the registersreflectthecount;

thatis,theday,date,andthetimethatwerecurrent

at the moment the halt commandwas issued.

All of the TIMEKEEPER registers are updated si-

multaneously.Ahalt will not interruptan update in

progress.Updatingis withina secondaftertheread

bit is reset to a ’0’.

Setting the Clock

The eighth bit of the control register is the WRITE

bit.Settingthe WRITEbit toa ’1’,liketheREADbit,

halts updates to the TIMEKEEPERregisters. The

usercan then loadthem withthe correctday,date,

and time data in 24 hour BCD format (see Table

10). ResettingtheWRITEbit to a’0’then transfers

the values of all time registers(7F9h-7FFh) to the

actual TIMEKEEPERcounters and allows normal

operationto resume.TheFTbitandthebitsmarked

as ’0’ in Table10 must be written to ’0’ to allow for

normal TIMEKEEPERand RAM operation.

See the Application Note AN923 ”TIMEKEEPER

rolling into the 21st century” for more information

on Century Rollover.

READ DATA

AT ANY ADDRESS

AI00607

ISDATA

COMPLEMENT

OFFIRST

READ

(BATTERY OK)

POWER-UP

YES

NO

WRITE DATA

COMPLEMENT BACK

TO SAME ADDRESS

READ DATA

AT SAME

ADDRESS AGAIN

NOTIFY SYSTEM

OF LOW BATTERY

(DATA MAY BE

CORRUPTED)

WRITE

ORIGINAL

DATA BACK TO

SAME ADDRESS

(BATTERY LOW)

CONTINUE

Figure 9. Checking the BOK Flag Status

9/15

M48T02, M48T12

相关PDF资料 |

PDF描述 |

|---|---|

| M50747-xxxFP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M50747 | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M50747-0F5SP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M50747-131SP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M50747-146SP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M48T02-70PC1 | 制造商:STMicroelectronics 功能描述:IC NVRAM 10 YR BATTERY 16K 48T02 |

| M48T02-70PC1TR | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5.0V, 16 Kbit (2Kb x 8) TIMEKEEPER㈢ SRAM |

| M48T08 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5V, 64Kbit (8 Kb x 8) TIMEKEEPER㈢ SRAM |

| M48T08_07 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5V, 64Kbit (8 Kb x 8) TIMEKEEPER㈢ SRAM |

| M48T08_10 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5 V, 64 Kbit (8 Kb x 8) TIMEKEEPER?? SRAM |

发布紧急采购,3分钟左右您将得到回复。