- 您现在的位置:买卖IC网 > PDF目录45050 > M48T212V-70MH1TR (STMICROELECTRONICS) 0 TIMER(S), REAL TIME CLOCK, PDSO44 PDF资料下载

参数资料

| 型号: | M48T212V-70MH1TR |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 时钟/数据恢复及定时提取 |

| 英文描述: | 0 TIMER(S), REAL TIME CLOCK, PDSO44 |

| 封装: | SNAPHAT, PLASTIC, SO-44 |

| 文件页数: | 5/23页 |

| 文件大小: | 150K |

| 代理商: | M48T212V-70MH1TR |

13/23

M48T212Y, M48T212V

TIMEKEEPER REGISTERS

The M48T212Y/V offers 16 internal registers

which contain TIMEKEEPER, Alarm, Watchdog,

Flag, and Control data. These registers are mem-

ory locations which contain external (user accessi-

ble) and internal copies of the data (usually

referred to as BiPORTTM TIMEKEEPER cells).

The external copies are independent of internal

functions except that they are updated periodically

by the simultaneous transfer of the incremented

internal copy. TIMEKEEPER and Alarm Registers

store data in BCD. Control, Watchdog and Flags

Registers store data in Binary Format.

CLOCK OPERATIONS

Reading the Clock

Updates to the TIMEKEEPER registers should be

halted before clock data is read to prevent reading

data in transition. Because the BiPORT TIME-

KEEPER cells in the RAM array are only data reg-

isters, and not the actual clock counters, updating

the registers can be halted without disturbing the

clock itself.

Updating is halted when a ‘ 1’ is written to the

READ bit, D6 in the Control Register (8h). As long

as a ‘1’ remains in that position, updating is halted.

After a halt is issued, the registers reflect the

count; that is, the day, date, and time that were

current at the moment the halt command was is-

sued.

All of the TIMEKEEPER registers are updated si-

multaneously. A halt will not interrupt an update in

progress. Updating occurs 1 second after the

READ bit is reset to a ‘ 0’.

Setting the Clock

Bit D7 of the Control Register (8h) is the WRITE

bit. Setting the WRITE bit to a ‘ 1’, like the READ

bit, halts updates to the TIMEKEEPER registers.

The user can then load them with the correct day,

date, and time data in 24 hour BCD format (see

Table 13).

Resetting the WRITE bit to a ‘0’ then transfers the

values of all time registers (Fh-9h, 1h) to the actual

TIMEKEEPER counters and allows normal opera-

tion to resume. After the WRITE bit is reset, the

next clock update will occur one second later.

Note: Upon power-up following a power failure,

the READ bit will automatically be set to a ‘1’. This

will prevent the clock from updating the TIME-

KEEPER registers, and will allow the user to read

the exact time of the power-down event.

Resetting the READ Bit to a ‘0’ will allow the clock

to update these registers with the current time.

The WRITE Bit will be reset to a ‘ 0’ upon power-

up.

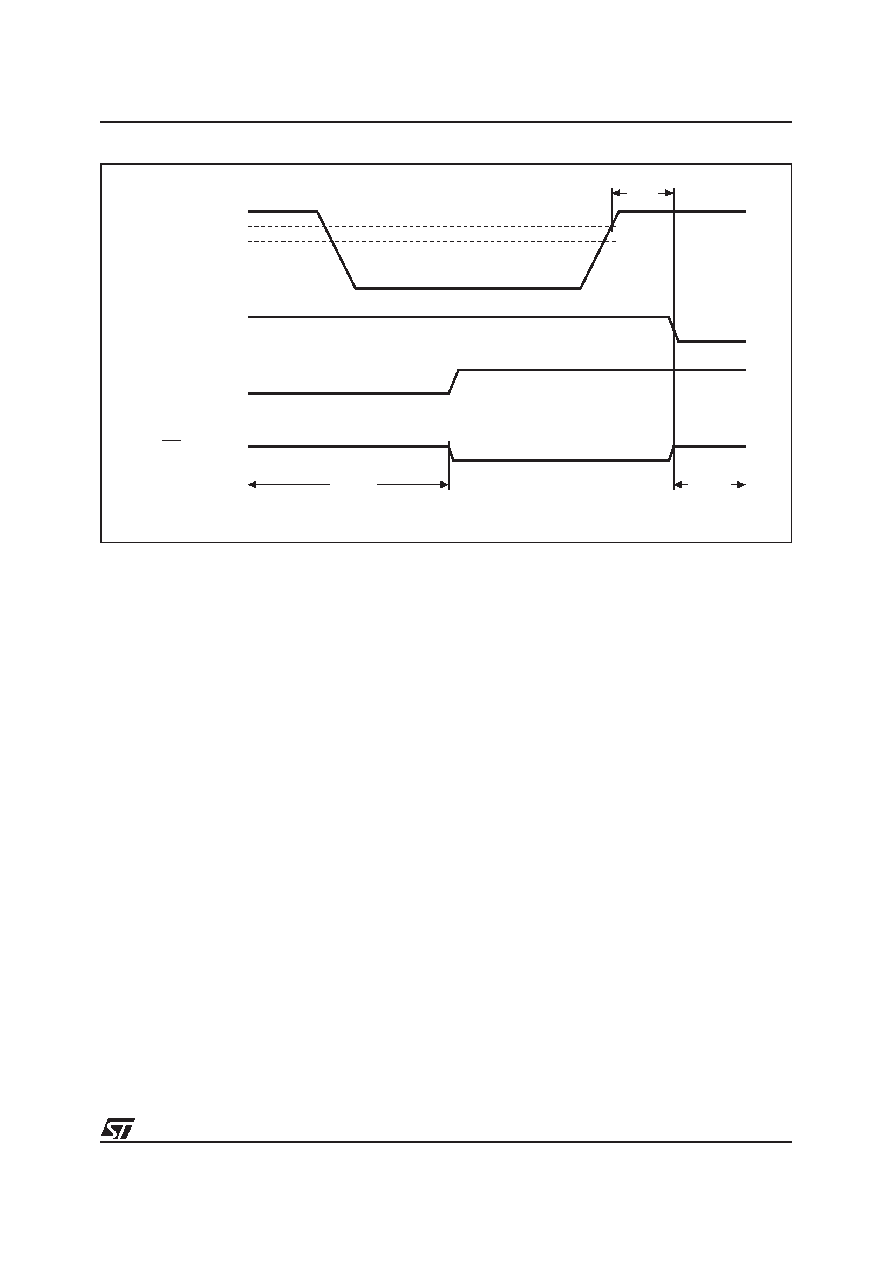

Figure 10. Back-Up Mode Alarm Waveforms

AI03622

VCC

IRQ/FT

HIGH-Z

VPFD (max)

VPFD (min)

AFE bit/ABE bit

AF bit in Flags Register

HIGH-Z

tREC

相关PDF资料 |

PDF描述 |

|---|---|

| M48T212V-85MH6 | 0 TIMER(S), REAL TIME CLOCK, PDSO44 |

| M48T212Y-70MH1TR | 0 TIMER(S), REAL TIME CLOCK, PDSO44 |

| M48T212Y-70MH1F | REAL TIME CLOCK, PDSO44 |

| M48T212Y-70MH1 | 0 TIMER(S), REAL TIME CLOCK, PDSO44 |

| M48T212V-85MH6E | REAL TIME CLOCK, PDSO44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M48T212V-70MH6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5V/3.3V TIMEKEEPER[ CONTROLLER |

| M48T212V-70MH6E | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5V/3.3V TIMEKEEPER CONTROLLER Supervisor |

| M48T212V-70MH6F | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5V/3.3V TIMEKEEPER CONTROLLER Supervisor |

| M48T212V-70MH6TR | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5V/3.3V TIMEKEEPER[ CONTROLLER |

| M48T212V-85MH1 | 功能描述:监控电路 SRAM TK 16X8 85ns RoHS:否 制造商:STMicroelectronics 监测电压数: 监测电压: 欠电压阈值: 过电压阈值: 输出类型:Active Low, Open Drain 人工复位:Resettable 监视器:No Watchdog 电池备用开关:No Backup 上电复位延迟(典型值):10 s 电源电压-最大:5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:UDFN-6 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。