- 您现在的位置:买卖IC网 > PDF目录45051 > M48T513Y-85CS1 (STMICROELECTRONICS) 0 TIMER(S), REAL TIME CLOCK, PDSO32 PDF资料下载

参数资料

| 型号: | M48T513Y-85CS1 |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 时钟/数据恢复及定时提取 |

| 英文描述: | 0 TIMER(S), REAL TIME CLOCK, PDSO32 |

| 封装: | SNAPHAT, PLASTIC, SO-44 |

| 文件页数: | 7/31页 |

| 文件大小: | 168K |

| 代理商: | M48T513Y-85CS1 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页

15/31

M48T513Y, M48T513V

Data Retention Mode

With valid VCC applied, the M48T513Y/V operates

as a conventional BYTEWIDE static RAM. Should

the supply voltage decay, the RAM will automati-

cally deselect, write protecting itself when VCC

falls between VPFD (max), VPFD (min) window. All

outputs become high impedance and all inputs are

treated as “don’t care.”

Note: A power failure during a WRITE cycle may

corrupt data at the current addressed location, but

does not jeopardize the rest of the RAM’s content.

At voltages below VPFD (min), the memory will be

in a write protected state, provided the VCC fall

time is not less than tF. The M48T513Y/V may re-

spond to transient noise spikes on VCC that cross

into the deselect window during the time the de-

vice is sampling VCC. Therefore, decoupling of the

power supply lines is recommended.

When VCC drops below VSO, the control circuit

switches power to the internal battery, preserving

data and powering the clock. The internal energy

source will maintain data in the M48T513Y/V for

an accumulated period of at least 10 years at room

temperature. As system power rises above VSO,

the battery is disconnected, and the power supply

is switched to external VCC. Deselect continues for

tREC after VCC reaches VPFD (max). For a further

more detailed review of lifetime calculations,

please see Application Note AN1012.

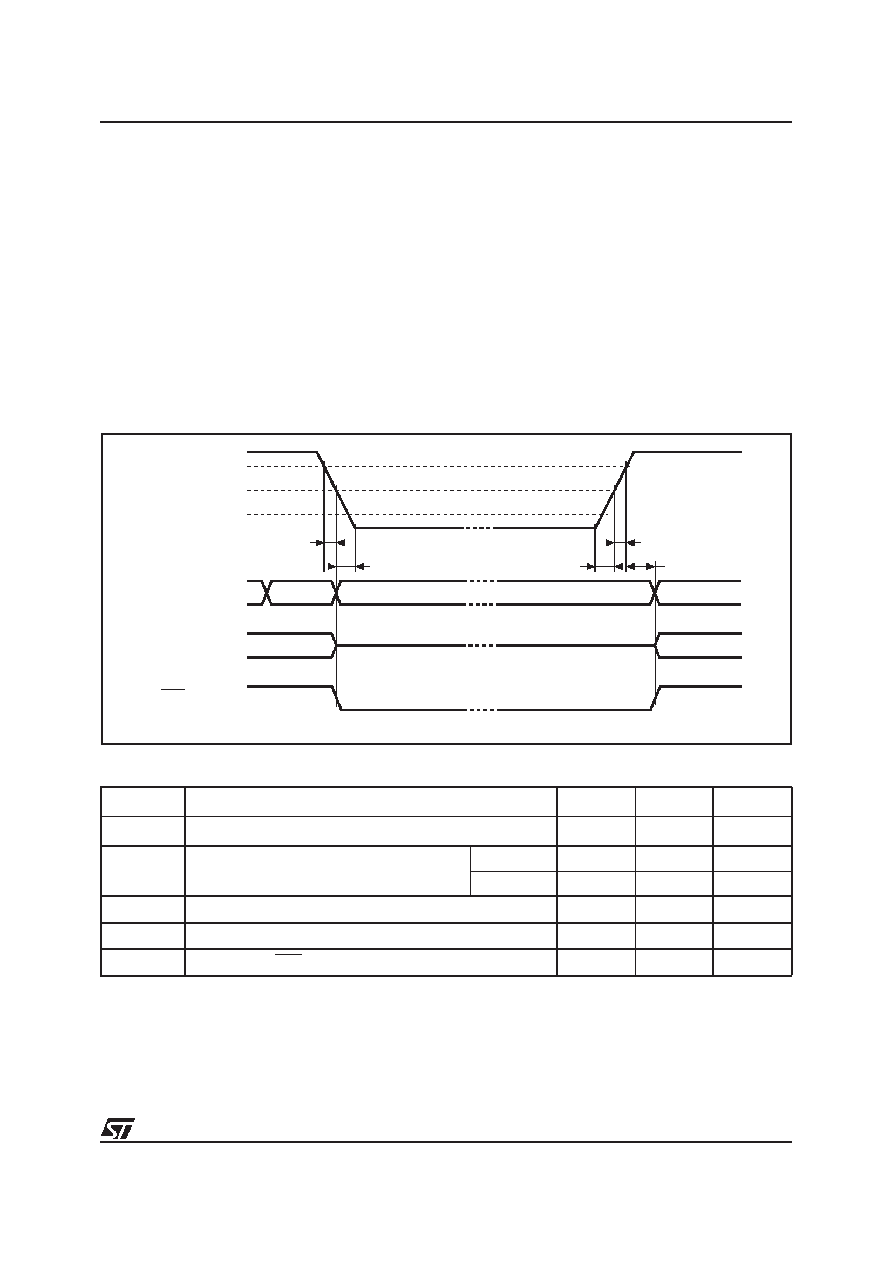

Figure 12. Power Down/Up Mode AC Waveforms

Table 9. Power Down/Up AC Characteristics

Note: 1. Valid for Ambient Operating Temperature: TA =0 to 70°C; VCC = 4.5 to 5.5V or 3.0 to 3.6V (except where noted).

2. VPFD (max) to VPFD (min) fall time of less than tF may result in deselection/write protection not occurring until 200ms after VCC pass-

es VPFD (min).

3. VPFD (min) to VSS fall time of less than tFB may cause corruption of RAM data.

Symbol

Parameter(1)

Min

Max

Unit

tF

(2)

VPFD (max) to VPFD (min) VCC Fall Time

300

s

tFB

(3)

VPFD (min) to VSS VCC Fall Time

M48T513Y

10

s

M48T513V

150

s

tR

VPFD (min) to VPFD (max) VCC Rise Time

0

s

tRB

VSS to VPFD (min) VCC Rise Time

1

s

tREC

VPFD (max) to RST High

40

200

ms

AI01805

VCC

INPUTS

OUTPUTS

DON’T CARE

HIGH-Z

tF

tFB

tR

tRB

VALID

RECOGNIZED

VPFD (max)

VPFD (min)

VSO

tREC

RST

相关PDF资料 |

PDF描述 |

|---|---|

| M48T559YMH1F | REAL TIME CLOCK, PDSO28 |

| M48T559YMH1 | 0 TIMER(S), REAL TIME CLOCK, PDSO28 |

| M48T58-70PC1 | 0 TIMER(S), REAL TIME CLOCK, PDIP28 |

| M48T58Y-70MH1E | 0 TIMER(S), REAL TIME CLOCK, PDSO28 |

| M48T58Y-70PC1TR | 0 TIMER(S), REAL TIME CLOCK, PDIP28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M48T513Y-85PM1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:3.3V-5V 4 Mbit 512Kb x8 TIMEKEEPER SRAM |

| M48T513YPM | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:3.3V-5V 4 Mbit 512Kb x8 TIMEKEEPER SRAM |

| M48T513YSH | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:3.3V-5V 4 Mbit 512Kb x8 TIMEKEEPER SRAM |

| M48T559 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64 Kbit 8Kb x8 TIMEKEEPER SRAM with ADDRESS/DATA MULTIPLEXED |

| M48T559Y | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64 Kbit 8Kb x8 TIMEKEEPER SRAM with ADDRESS/DATA MULTIPLEXED |

发布紧急采购,3分钟左右您将得到回复。