- 您现在的位置:买卖IC网 > PDF目录45051 > M48T513Y-85CS1 (STMICROELECTRONICS) 0 TIMER(S), REAL TIME CLOCK, PDSO32 PDF资料下载

参数资料

| 型号: | M48T513Y-85CS1 |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 时钟/数据恢复及定时提取 |

| 英文描述: | 0 TIMER(S), REAL TIME CLOCK, PDSO32 |

| 封装: | SNAPHAT, PLASTIC, SO-44 |

| 文件页数: | 8/31页 |

| 文件大小: | 168K |

| 代理商: | M48T513Y-85CS1 |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页

M48T513Y, M48T513V

16/31

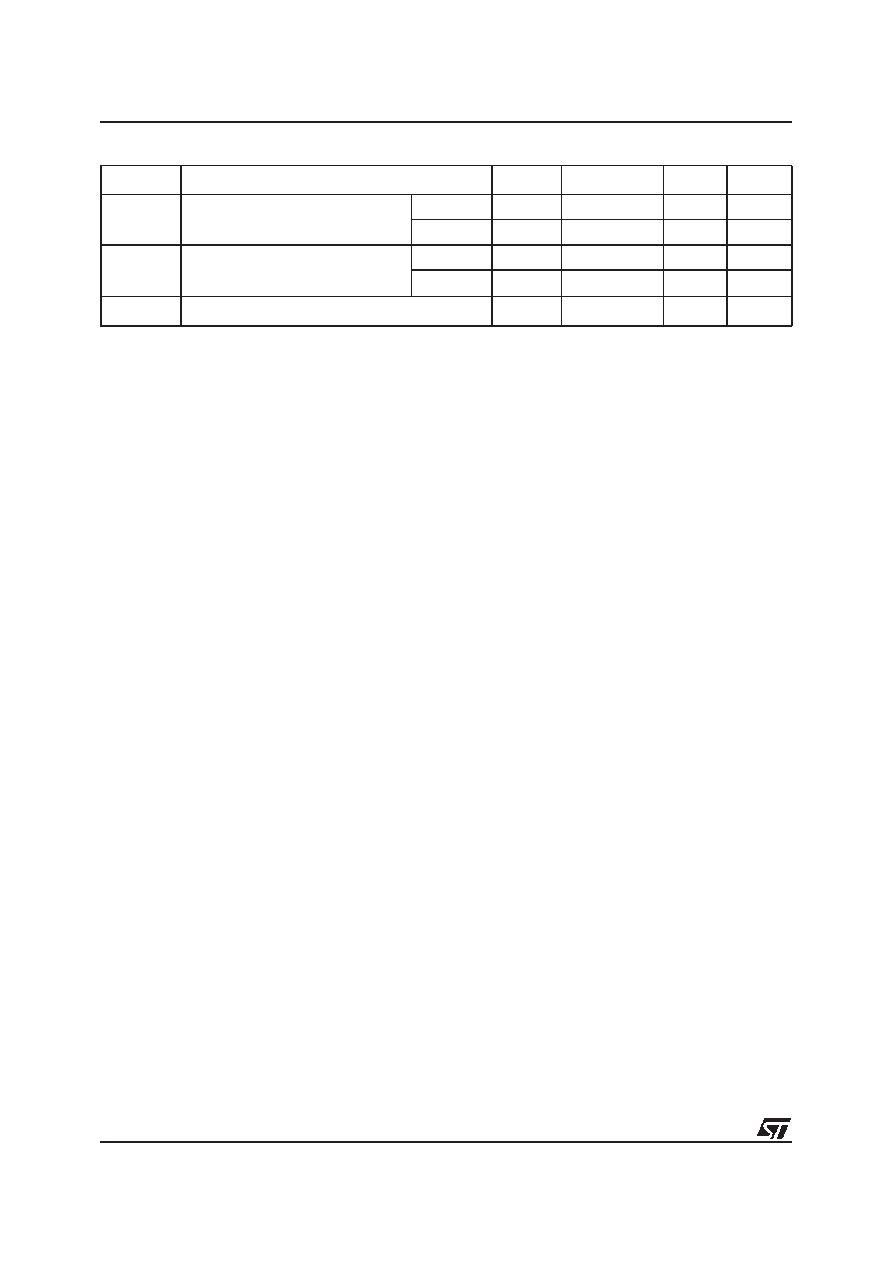

Table 10. Power Down/Up Trip Points DC Characteristics

Note: 1. Valid for Ambient Operating Temperature: TA =0 to 70°C; VCC = 4.5 to 5.5V or 3.0 to 3.6V (except where noted).

2. All voltages referenced to VSS.

3. At 25

°C.

CLOCK OPERATIONS

TIMEKEEPER Registers

The M48T513Y/V offers 16 internal registers

which contain TIMEKEEPER, Alarm, Watchdog,

Interrupt, Flag, and Control data (see Table 11,

page 17). These registers are memory locations

which contain external (user accessible) and inter-

nal copies of the data (usually referred to as Bi-

PORT

TIMEKEEPER cells). The external

copies are independent of internal functions ex-

cept that they are updated periodically by the si-

multaneous transfer of the incremented internal

copy. TIMEKEEPER and Alarm Registers store

data in BCD.

Reading the Clock

Updates to the TIMEKEEPER registers should

be halted before clock data is read to prevent

reading data in transition. The BiPORT

TIME-

KEEPER cells in the RAM array are only data reg-

isters and not the actual clock counters, so

updating the registers can be halted without dis-

turbing the clock itself.

Updating is halted when a ’1’ is written to the

READ Bit, D6 in the Control Register (7FFF8h). As

long as a ’1’ remains in that position, updating is

halted. After a halt is issued, the registers reflect

the count; that is, the day, date, and time that were

current at the moment the halt command was is-

sued. All of the TIMEKEEPER registers are updat-

ed simultaneously. A halt will not interrupt an

update in progress. Updating occurs 1 second af-

ter the READ Bit is reset to a ’0.’

Setting the Clock

Bit D7 of the Control Register (7FFF8h) is the

WRITE Bit. Setting the WRITE Bit to a ’1’, like the

READ Bit, halts updates to the TIMEKEEPER reg-

isters. The user can then load them with the cor-

rect day, date, and time data in 24 hour BCD

format (see Table Figure 11, page 17).

Resetting the WRITE Bit to a ’0’ then transfers the

values of all time registers (7FFFFh-7FFF9h,

7FFF1h) to the actual TIMEKEEPER counters and

allows normal operation to resume. After the

WRITE Bit is reset, the next clock update will occur

approximately one second later.

Note: Upon power-up following a power failure,

both the WRITE Bit and the READ Bit will be reset

to ’0.’

Stopping and Starting the Oscillator

The oscillator may be stopped at any time. If the

device is going to spend a significant amount of

time on the shelf, the oscillator can be turned off to

minimize current drain on the battery. The STOP

Bit is located at Bit D7 within 7FFF9h. Setting it to

a ’1’ stops the oscillator. When reset to a ’0,’ the

M48T513Y/V oscillator starts within one second.

Note: It is not necessary to set the WRITE Bit

when setting or resetting the FREQUENCY TEST

Bit (FT) or the STOP Bit (ST).

Symbol

Parameter(1,2)

Min

Typ

Max

Unit

VPFD

Power-fail Deselect Voltage

M48T513Y

4.2

4.35

4.5

V

M48T513V

2.7

2.9

3.0

V

VSO

Batter y Back-up Switchover Voltage

M48T513Y

3.0

V

M48T513V

VPFD –100mV

tDR

(3)

Expected Data Retention Time

10

YEARS

相关PDF资料 |

PDF描述 |

|---|---|

| M48T559YMH1F | REAL TIME CLOCK, PDSO28 |

| M48T559YMH1 | 0 TIMER(S), REAL TIME CLOCK, PDSO28 |

| M48T58-70PC1 | 0 TIMER(S), REAL TIME CLOCK, PDIP28 |

| M48T58Y-70MH1E | 0 TIMER(S), REAL TIME CLOCK, PDSO28 |

| M48T58Y-70PC1TR | 0 TIMER(S), REAL TIME CLOCK, PDIP28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M48T513Y-85PM1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:3.3V-5V 4 Mbit 512Kb x8 TIMEKEEPER SRAM |

| M48T513YPM | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:3.3V-5V 4 Mbit 512Kb x8 TIMEKEEPER SRAM |

| M48T513YSH | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:3.3V-5V 4 Mbit 512Kb x8 TIMEKEEPER SRAM |

| M48T559 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64 Kbit 8Kb x8 TIMEKEEPER SRAM with ADDRESS/DATA MULTIPLEXED |

| M48T559Y | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64 Kbit 8Kb x8 TIMEKEEPER SRAM with ADDRESS/DATA MULTIPLEXED |

发布紧急采购,3分钟左右您将得到回复。