- 您现在的位置:买卖IC网 > PDF目录180222 > M5-320/120-15HC (LATTICE SEMICONDUCTOR CORP) Fifth Generation MACH Architecture PDF资料下载

参数资料

| 型号: | M5-320/120-15HC |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | Fifth Generation MACH Architecture |

| 中文描述: | EE PLD, 15 ns, PQFP160 |

| 封装: | HEAT SINK, PLASTIC, QFP-160 |

| 文件页数: | 34/47页 |

| 文件大小: | 1145K |

| 代理商: | M5-320/120-15HC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页当前第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页

4

MACH 5 Family

Advanced power management options allow designers to incrementally reduce power while

maintaining the level of performance needed for today’s complex designs. I/O safety features

allow for mixed-voltage design, and both the 3.3-V and the 5-V device versions are in-system

programmable through an IEEE 1149.1 Test Access Port (TAP) interface.

FUNCTIONAL DESCRIPTION

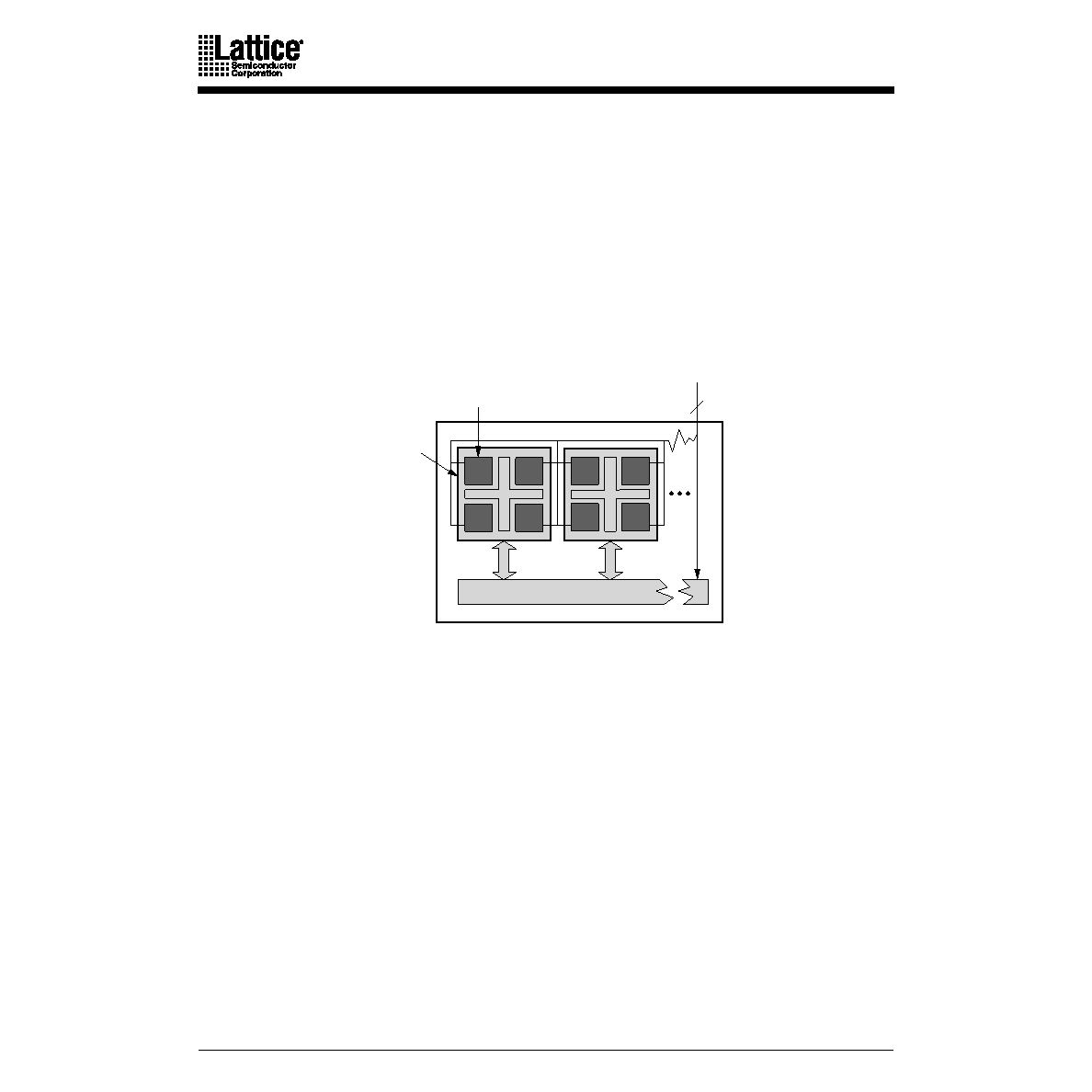

The MACH 5 architecture consists of PAL blocks connected by two levels of interconnect. The block

interconnect

provides routing among 4 PAL blocks. This grouping of PAL blocks joined by the

block interconnect is called a segment. The second level of interconnect, the segment

interconnect

, ties all of the segments together. The only logic difference between any two MACH

5 devices is the number of segments. Therefore, once a designer is familiar with one device,

consistent performance can be expected across the entire family. All devices have four clock pins

available which can also be used as logic inputs.

The MACH 5 PAL blocks consist of the elements listed below (Figure 2). While each PAL block

resembles an independent PAL device, it has superior control and logic generation capabilities.

x

I/O cells

x

Product-term array and Logic Allocator

x

Macrocells

x

Register control generator

x

Output enable generator

I/O Cells

The I/Os associated with each PAL block have a path directly back to that PAL block called

local

feedback. If the I/O is used in another PAL block, the interconnect feeder assigns a block interconnect

line to that signal. The interconnect feeder acts as an input switch matrix. The block and segment

interconnects provide connections between any two signals in a device. The

block feeder assigns

block interconnect lines and local feedback lines to the PAL block inputs.

Block

Interconnect

4

CLK

Block:

16 MCs

Segment:

4 Blocks

Segment Interconnect

20446G-001

Figure 1. MACH 5 Block Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| M5-320/120-15HI | Fifth Generation MACH Architecture |

| M5-320/120-20HI | Fifth Generation MACH Architecture |

| M5-320/160-10HC | Fifth Generation MACH Architecture |

| M5-320/160-10HI | Fifth Generation MACH Architecture |

| M5-320/160-12HC | Fifth Generation MACH Architecture |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M53-20171HLF | 制造商:BITECH 制造商全称:Bi technologies 功能描述:High Power Low Cost Inductors |

| M53-20171VLF | 制造商:BITECH 制造商全称:Bi technologies 功能描述:High Power Low Cost Inductors |

| M53-20190HLF | 制造商:BITECH 制造商全称:Bi technologies 功能描述:High Power Low Cost Inductors |

| M53-20190VLF | 制造商:BITECH 制造商全称:Bi technologies 功能描述:High Power Low Cost Inductors |

| M53-20350HLF | 制造商:BITECH 制造商全称:Bi technologies 功能描述:High Power Low Cost Inductors |

发布紧急采购,3分钟左右您将得到回复。