- 您现在的位置:买卖IC网 > PDF目录180222 > M5-320/120-15HC (LATTICE SEMICONDUCTOR CORP) Fifth Generation MACH Architecture PDF资料下载

参数资料

| 型号: | M5-320/120-15HC |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | Fifth Generation MACH Architecture |

| 中文描述: | EE PLD, 15 ns, PQFP160 |

| 封装: | HEAT SINK, PLASTIC, QFP-160 |

| 文件页数: | 43/47页 |

| 文件大小: | 1145K |

| 代理商: | M5-320/120-15HC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页当前第43页第44页第45页第46页第47页

MACH 5 Family

5

Product-Term Array and Logic Allocator

The product-term array uses the same sum-of-products architecture as PAL devices and consists of

32 inputs (plus their complements) and 64 product terms arranged in 16

clusters. A cluster is a sum-

of-products function with either 3 of 4 product terms.

Logic allocators assign the clusters to macrocells. Each macrocell can accept up to eight clusters of

three or four product terms, but a given cluster can only be steered to one macrocell (Table 4). If

only three product terms in a cluster are steered, the fourth can be used as an input to an XOR

gate for separate logic generation and/or polarity control.

The

wide logic allocator is comprised of all 16 of the individual logic allocators and acts as an output

switch matrix by reassigning logic to macrocells to retain pinout as designs change. The logic

allocation scheme in the MACH 5 device allows for the implementation of large equations (up to

32 product terms) with only one pass through the logic array.

Table 4. Product Term Steering Options for PT Clusters and Macrocells

Macrocell

Available Clusters

Macrocell

Available Clusters

M0

C0, C1, C2, C3, C4

M8

C5, C6, C7, C8, C9, C10, C11, C12

M1

C0, C1, C2, C3, C4, C5

M9

C6, C7, C8, C9, C10, C11, C12, C13

M2

C0, C1, C2, C3, C4, C5, C6

M10

C7, C8, C9, C10, C11, C12, C13, C14

M3

C0, C1, C2, C3, C4, C5, C6, C7

M11

C8, C9, C10, C11, C12, C13, C14, C15

M4

C0, C1, C2, C3, C4, C5, C6, C7

M12

C8, C9, C10, C11, C12, C13, C14, C15

M5

C1, C2, C3, C4, C5, C6, C7, C8

M13

C9, C10, C11, C12, C13, C14, C15

M6

C2, C3, C4, C5, C6, C7, C8, C9

M14

C10, C11, C12, C13, C14, C15

M7

C3, C4, C5, C6, C7, C8, C9, C10

M15

C11, C12, C13, C14, C15

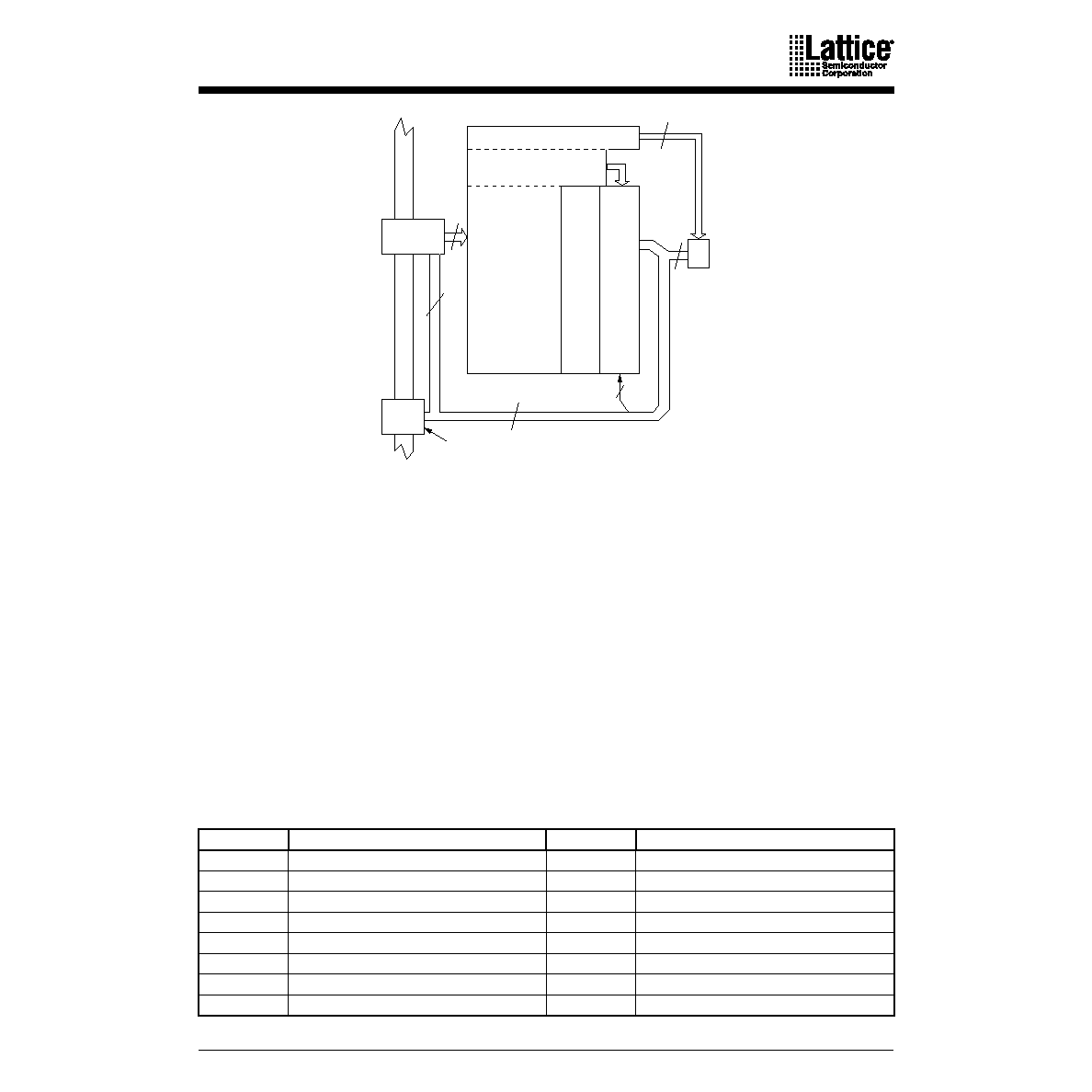

Block

Interconnect

Interconnect Feeder

Block

Feeder

32

I/Os

16

2

Macrocells

Logic

Alocator

Control Generator

OE Generator

Product-term

Array

32

Input Register

Path

2

Local

Feedback

20446G-002

Figure 2. PAL Block Structure

相关PDF资料 |

PDF描述 |

|---|---|

| M5-320/120-15HI | Fifth Generation MACH Architecture |

| M5-320/120-20HI | Fifth Generation MACH Architecture |

| M5-320/160-10HC | Fifth Generation MACH Architecture |

| M5-320/160-10HI | Fifth Generation MACH Architecture |

| M5-320/160-12HC | Fifth Generation MACH Architecture |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M53-20171HLF | 制造商:BITECH 制造商全称:Bi technologies 功能描述:High Power Low Cost Inductors |

| M53-20171VLF | 制造商:BITECH 制造商全称:Bi technologies 功能描述:High Power Low Cost Inductors |

| M53-20190HLF | 制造商:BITECH 制造商全称:Bi technologies 功能描述:High Power Low Cost Inductors |

| M53-20190VLF | 制造商:BITECH 制造商全称:Bi technologies 功能描述:High Power Low Cost Inductors |

| M53-20350HLF | 制造商:BITECH 制造商全称:Bi technologies 功能描述:High Power Low Cost Inductors |

发布紧急采购,3分钟左右您将得到回复。