- 您现在的位置:买卖IC网 > PDF目录180233 > M5M5V416CWG-70HI 256K X 16 STANDARD SRAM, 70 ns, PBGA48 PDF资料下载

参数资料

| 型号: | M5M5V416CWG-70HI |

| 元件分类: | SRAM |

| 英文描述: | 256K X 16 STANDARD SRAM, 70 ns, PBGA48 |

| 封装: | 7 X 8.50 MM, 0.75 MM PITCH, CSP-48 |

| 文件页数: | 4/9页 |

| 文件大小: | 265K |

| 代理商: | M5M5V416CWG-70HI |

M5M5V416CWG -55HI, -70HI

2003.08.21

Ver. 7.0

4194304-BIT (262144-WORD BY 16-BIT) CMOS STATIC RAM

RENESAS LSIs

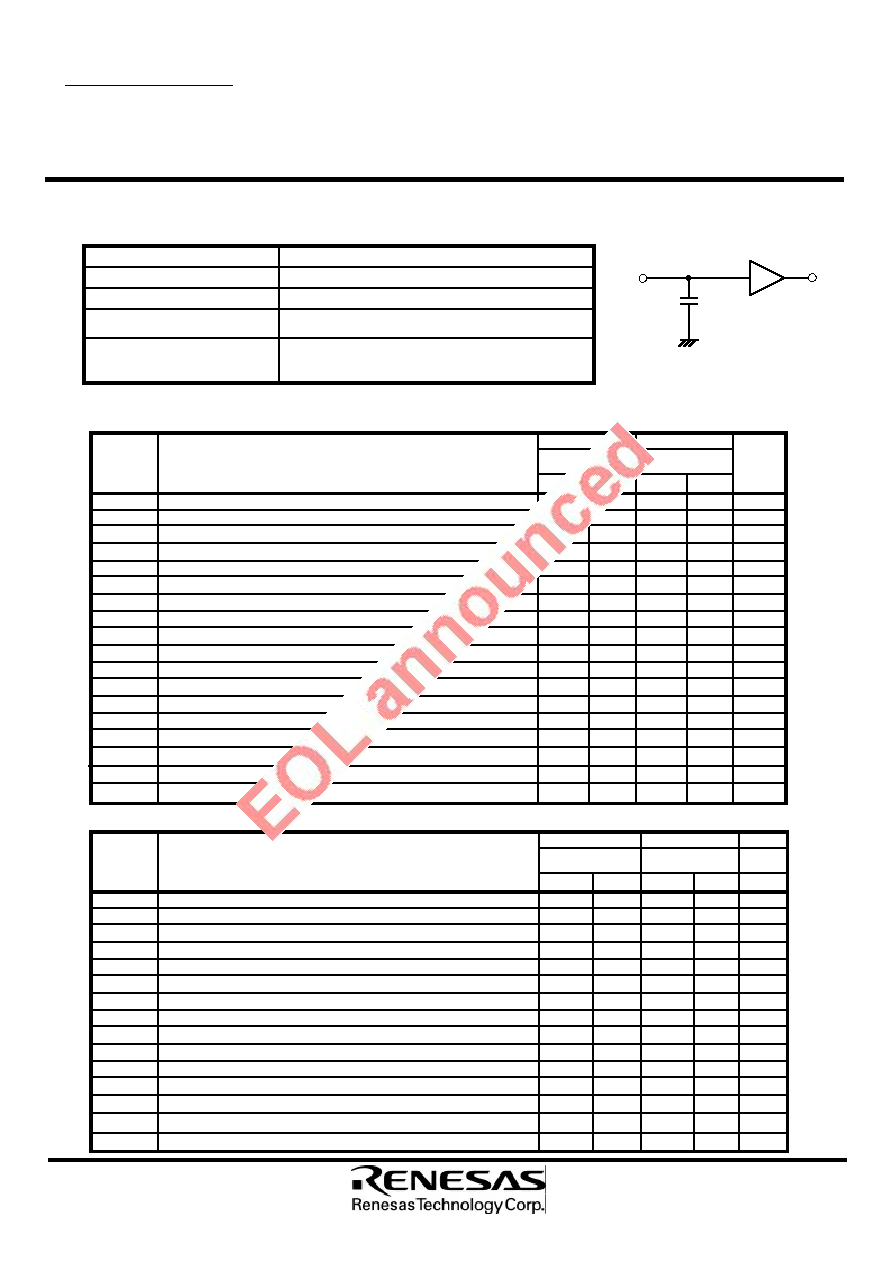

AC ELECTRICAL CHARACTERISTICS

(Vcc=2.7 ~ 3.6V, unless noted. )

Input rise time and f all time

Ref erence lev el

Output loads

2.7~3.6V

VIH=2.4V, VIL=0.2V

Transition is measured ±200mV from

steady state voltage.(for ten,tdis)

5ns

Fig.1,CL=30pF

CL=5pF (for ten,tdis)

(1) TEST CONDITIONS

Supply v oltage

Input pulse

1TTL

CL

DQ

Fig.1 Output load

Including scope and

jig capacitance

tCR

ta(S1)

ta(OE)

tdis(S1)

tdis(OE)

ten(S1)

ten(OE)

tV(A)

ta(A)

10

30

ta(BC1)

ta(BC2)

tdis(BC1)

tdis(BC2)

ten(BC1)

ten(BC2)

55

20

5

10

ta(S2)

55

ten(S2)

10

tdis(S2)

20

55

55HI

4

tsu(A-WH)

tCW

tw(W)

tsu(A)

tsu(S1)

tsu(D)

th(D)

trec(W)

tdis(W)

tdis(OE)

ten(W)

ten(OE)

tsu(BC1)

tsu(BC2)

tsu(S2)

20

55

45

0

50

5

50

30

0

50

Symbol

Parameter

Read cy cle time

Limits

Address access time

Chip select 1 access time

Chip select 2 access time

By te control 1 access time

By te control 2 access time

Output enable access time

Output disable time aft er S2 low

Output disable time aft er S1# high

Output disable time aft er BC1# high

Max

Min

(2) READ CYCLE

Output disable time aft er BC2# high

Output disable time aft er OE# high

Output enable time af ter S1# low

Output enable time af ter S2 high

Output enable time af ter BC1# low

Output enable time af ter BC2# low

Output enable time af ter OE# low

Data v alid time after address

(3) WRITE CYCLE

Max

Min

Limits

Write cy cle time

Write pulse width

Address setup time

Address setup time with respect to W#

By te control 1 setup time

By te control 2 setup time

Chip select 1 setup time

Chip select 2 setup time

Data setup time

Data hold time

Write recov ery time

Output disable time f rom W# low

Output disable time f rom OE# high

Output enable time f rom W# high

Output enable time f rom OE# low

Symbol

Parameter

VOH=VOL=1.50V

55HI

ns

10

35

ns

70

25

5

10

ns

70

10

ns

25

70

70HI

ns

25

70

55

0

60

5

60

35

0

60

Limits

Max

Min

Units

Max

Min

Limits

Units

70HI

相关PDF资料 |

PDF描述 |

|---|---|

| M5R24TLJ800.0000MHZ | CRYSTAL OSCILLATOR, CLOCK, 800 MHz, LVDS OUTPUT |

| M5R28TPJ-R800.0000MHZ | CRYSTAL OSCILLATOR, CLOCK, 800 MHz, PECL OUTPUT |

| M5R75XQJ0.7500MHZ | CRYSTAL OSCILLATOR, CLOCK, 0.75 MHz, PECL OUTPUT |

| M5R18THJ-R0.7500MHZ | CRYSTAL OSCILLATOR, CLOCK, 0.75 MHz, LVDS OUTPUT |

| M5R13RHJ-R0.7500MHZ | CRYSTAL OSCILLATOR, CLOCK, 0.75 MHz, LVDS OUTPUT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M5M5V416WG-70LI | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:4194304-BIT (262144-WORD BY 16-BIT) CMOS STATIC RAM |

| M5M5V4R01J-12 | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:4194304-BIT (4194304-WORD BY 1-BIT) CMOS STATIC RAM |

| M5M5V4R01J-15 | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:4194304-BIT (4194304-WORD BY 1-BIT) CMOS STATIC RAM |

| M5M5V4R04J-12 | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:4194304-BIT (1048576-WORD BY 4-BIT) CMOS STATIC RAM |

| M5M5V4R04J-15 | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:4194304-BIT (1048576-WORD BY 4-BIT) CMOS STATIC RAM |

发布紧急采购,3分钟左右您将得到回复。