- 您现在的位置:买卖IC网 > PDF目录296428 > M68AW512DL70ZB6F (STMICROELECTRONICS) 512K X 16 STANDARD SRAM, 70 ns, PBGA48 PDF资料下载

参数资料

| 型号: | M68AW512DL70ZB6F |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | SRAM |

| 英文描述: | 512K X 16 STANDARD SRAM, 70 ns, PBGA48 |

| 封装: | 8 X 10 MM, 0.75 MM PITCH, ROHS COMPLIANT, TFBGA-48 |

| 文件页数: | 10/23页 |

| 文件大小: | 427K |

| 代理商: | M68AW512DL70ZB6F |

Obsolete

Product(s)

- Obsolete

Product(s)

M68AW512D

18/23

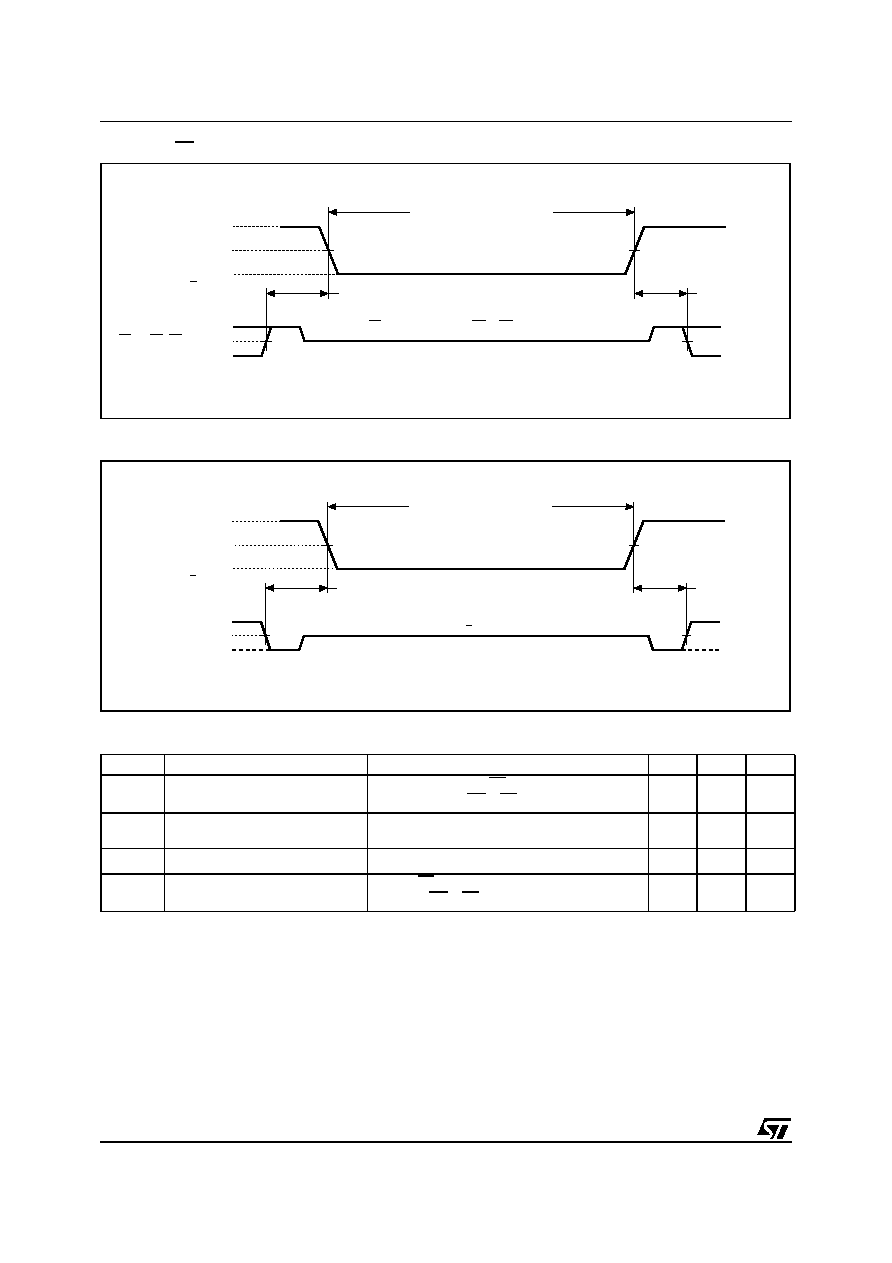

Figure 13. E1 Controlled, Low VCC Data Retention AC Waveforms

Figure 14. E2 Controlled, Low VCC Data Retention AC Waveforms

Table 9. Low VCC Data Retention Characteristics

Note: 1. All other Inputs at VIH ≥ VCC –0.2V or VIL ≤ 0.2V.

2. Tested initially and after any design or process that may affect these parameters.

tAVAV is Read cycle time.

3. No input may exceed VCC +0.2V.

Symbol

Parameter

Test Condition

Min

Max

Unit

ICCDR

(1)

Supply Current (Data Retention)

VCC = 1.5V, E1 ≥ VCC –0.2V or

E2

≤ 0.2V or UB = LB ≥ VCC –0.2V, f = 0

30

A

tCDR

(1,2)

Chip Deselected to Data

Retention Time

0ns

tR

(2)

Operation Recovery Time

tAVAV

ns

VDR

(1)

Supply Voltage (Data Retention)

E1

≥ VCC –0.2V or E2 ≤ 0.2V or

UB = LB

≥ VCC –0.2V, f = 0

1.5

V

AI05985

DATA RETENTION MODE

tR

3.6V

tCDR

VCC

2.7V

VDR > 1.5V

E1 or UB/LB

E1

≥ VDR – 0.2V or UB = LB ≥ VDR – 0.2V

AI05986c

DATA RETENTION MODE

tR

3.6V

tCDR

VCC

2.7V

VDR > 1.5V

E2

E2 < 0.2V

相关PDF资料 |

PDF描述 |

|---|---|

| M701-720442 | TELECOM AND DATACOM CONNECTOR |

| M701-820442 | TELECOM AND DATACOM CONNECTOR |

| M74HC154B1N | HC/UH SERIES, OTHER DECODER/DRIVER, INVERTED OUTPUT, PDIP24 |

| M74HC266M1R | HC/UH SERIES, QUAD 2-INPUT XNOR GATE, PDSO14 |

| M74HC393 | DUAL BINARY COUNTER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M68AW512DL70ZB6T | 制造商:STMicroelectronics 功能描述: |

| M68AW512DN55ZB1T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8 Mbit 512K x16 3.0V Asynchronous SRAM |

| M68AW512DN55ZB6 | 制造商:STMicroelectronics 功能描述: |

| M68AW512DN55ZB6T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8 Mbit 512K x16 3.0V Asynchronous SRAM |

| M68AW512DN70ZB1T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8 Mbit 512K x16 3.0V Asynchronous SRAM |

发布紧急采购,3分钟左右您将得到回复。