- 您现在的位置:买卖IC网 > PDF目录365230 > MACH220-20 (ADVANCED MICRO DEVICES INC) High-Density EE CMOS Programmable Logic PDF资料下载

参数资料

| 型号: | MACH220-20 |

| 厂商: | ADVANCED MICRO DEVICES INC |

| 元件分类: | PLD |

| 英文描述: | High-Density EE CMOS Programmable Logic |

| 中文描述: | EE PLD, PQCC68 |

| 文件页数: | 28/33页 |

| 文件大小: | 230K |

| 代理商: | MACH220-20 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页第29页第30页第31页第32页第33页

AMD

28

MACH220-10/12/15/20

USING PRELOAD AND OBSERVABILITY

In order to be testable, a circuit must be both controllable

and observable. To achieve this, the MACH devices

incorporate register preload and observability.

In preload mode, each flip-flop in the MACH device can

be loaded from the I/O pins, in order to perform

functional testing of complex state machines. Register

preload makes it possible to run a series of tests from a

known starting state, or to load illegal states and test for

proper recovery. This ability to control the MACH

device’s internal state can shorten test sequences,

since it is easier to reach the state of interest.

The observability function makes it possible to see the

internal state of the buried registers during test by

overriding each register’s output enable and activating

the output buffer. The values stored in output and buried

registers can then be observed on the I/O pins. Without

this feature, a thorough functional test would be

impossible for any designs with buried registers.

While the implementation of the testability features is

fairly straightforward, care must be taken in certain

instances to insure valid testing.

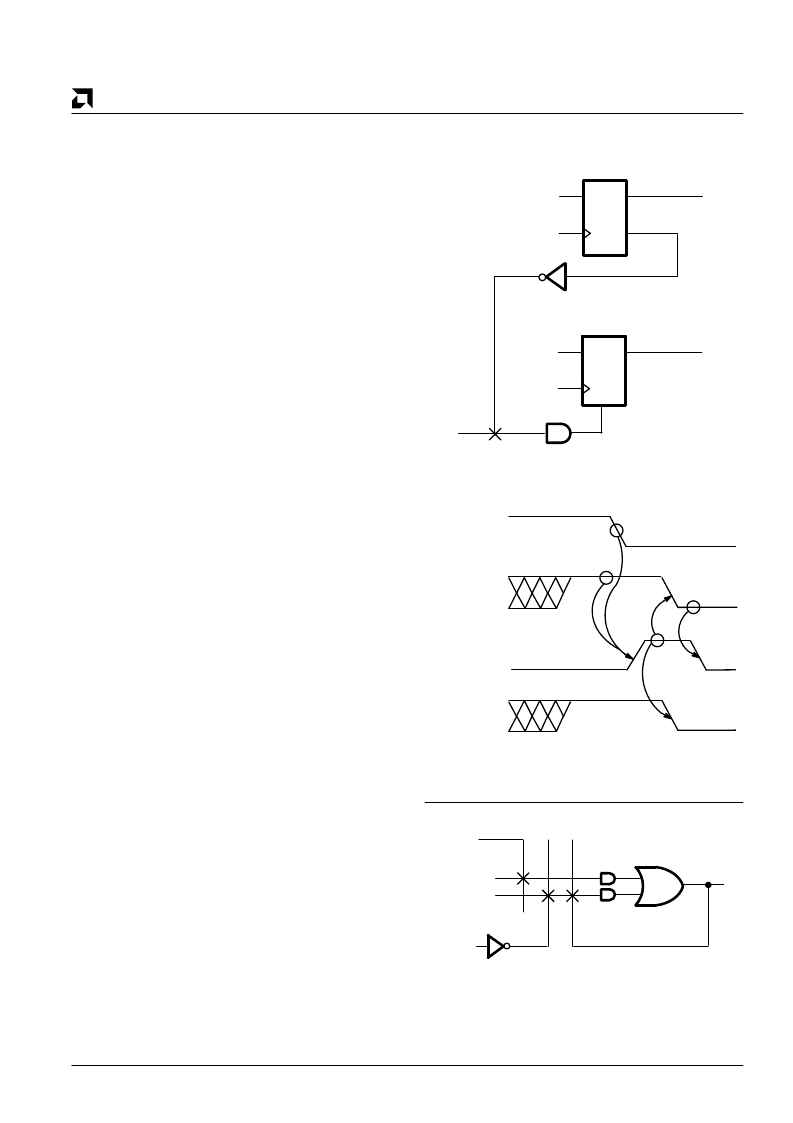

One case involves asynchronous reset and preset. If the

MACH registers drive asynchronous reset or preset

lines and are preloaded in such a way that reset or

preset are asserted, the reset or preset may remove the

preloaded data. This is illustrated in Figure 2. Care

should be taken when planning functional tests, so that

states that will cause unexpected resets and presets are

not preloaded.

Another case to be aware of arises in testing combinato-

rial logic. When an output is configured as combinato-

rial, the observability feature forces the output into

registered mode. When this happens, all product terms

are forced to zero, which eliminates all combinatorial

data. For a straight combinatorial output, the correct

value will be restored after the preload or observe

function, and there will be no problem. If the function

implements a combinatorial latch, however, it relies on

feedback to hold the correct value, as shown in Figure 3.

As this value may change during the preload or observe

operation, you cannot count on the data being correct

after the operation. To insure valid testing in these

cases, outputs that are combinatorial latches should not

be tested immediately following a preload or observe

sequence, but should first be restored to a known state.

All MACH 2 devices support both preload and

observability.

Contact individual programming vendors in order to

verify programmer support.

AR

Figure 2. Preload/Reset Conflict

Q

1

On

Off

Preload

Mode

Q

2

AR

Preloaded

HIGH

D

Q

Q

1

D

Q

AR

Preloaded

HIGH

Q

2

14130I-26

Figure 3. Combinatorial Latch

Set

Reset

14130I-27

相关PDF资料 |

PDF描述 |

|---|---|

| MACH220-20JI | High-Density EE CMOS Programmable Logic |

| MAX542 | Quadruple Bus Buffer Gate With 3-State Outputs 14-PDIP -40 to 85 |

| MAX542ACPD | +5V, Serial-Input, Voltage-Output, 16-Bit DACs |

| MAX542ACSD | +5V, Serial-Input, Voltage-Output, 16-Bit DACs |

| MAX542AEPD | +5V, Serial-Input, Voltage-Output, 16-Bit DACs |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MACH220-20JC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MACH220-20JI | 制造商:AMD 制造商全称:Advanced Micro Devices 功能描述:High-Density EE CMOS Programmable Logic |

| MACH221-10JC | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:High-Performance EE CMOS Programmable Logic |

| MACH221-10JI | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:High-Performance EE CMOS Programmable Logic |

| MACH221-12JC | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:High-Performance EE CMOS Programmable Logic |

发布紧急采购,3分钟左右您将得到回复。