- 您现在的位置:买卖IC网 > PDF目录383310 > MAX1127EGK (MAXIM INTEGRATED PRODUCTS INC) Quad, 12-Bit, 65Msps, 1.8V ADC with Serial LVDS Outputs PDF资料下载

参数资料

| 型号: | MAX1127EGK |

| 厂商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分类: | ADC |

| 英文描述: | Quad, 12-Bit, 65Msps, 1.8V ADC with Serial LVDS Outputs |

| 中文描述: | 4-CH 12-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, QCC68 |

| 封装: | 10 X 10 MM, 0.90 MM HEIGHT, MO-220, QFN-68 |

| 文件页数: | 22/25页 |

| 文件大小: | 1661K |

| 代理商: | MAX1127EGK |

M

Quad, 12-Bit, 65Msps, 1.8V ADC with

Serial LVDS Outputs

22

______________________________________________________________________________________

Global Power-Down (PDALL)

PDALL controls the power-down mode of all channels

and the internal reference circuitry. Drive PDALL high

to enable global power-down. In global power-down

mode, the output impedance of all the LVDS/SLVS out-

puts is approximately 378

, if DT is low. The output

impedance of the differential LVDS/SLVS outputs is

100

when DT is high. See the

Electrical

Characteristics

table for typical supply currents with

global power-down. The following list shows the state of

the analog inputs and digital outputs in global power-

down mode:

IN_P, IN_N analog inputs are disconnected from the

internal input amplifier.

REFIO has > 1M

resistance to GND.

OUT_P, OUT_N, CLKOUTP, CLKOUTN, FRAMEP,

and FRAMEN have approximately 378

between the

output pairs when DT is low. When DT is high, the dif-

ferential output pairs have 100

between each pair.

When operating from the internal reference, the wake-

up time from global power-down is typically 132μs.

When using an external reference, the wake-up time is

dependent on the external reference drivers.

Applications Information

Using Transformer Coupling

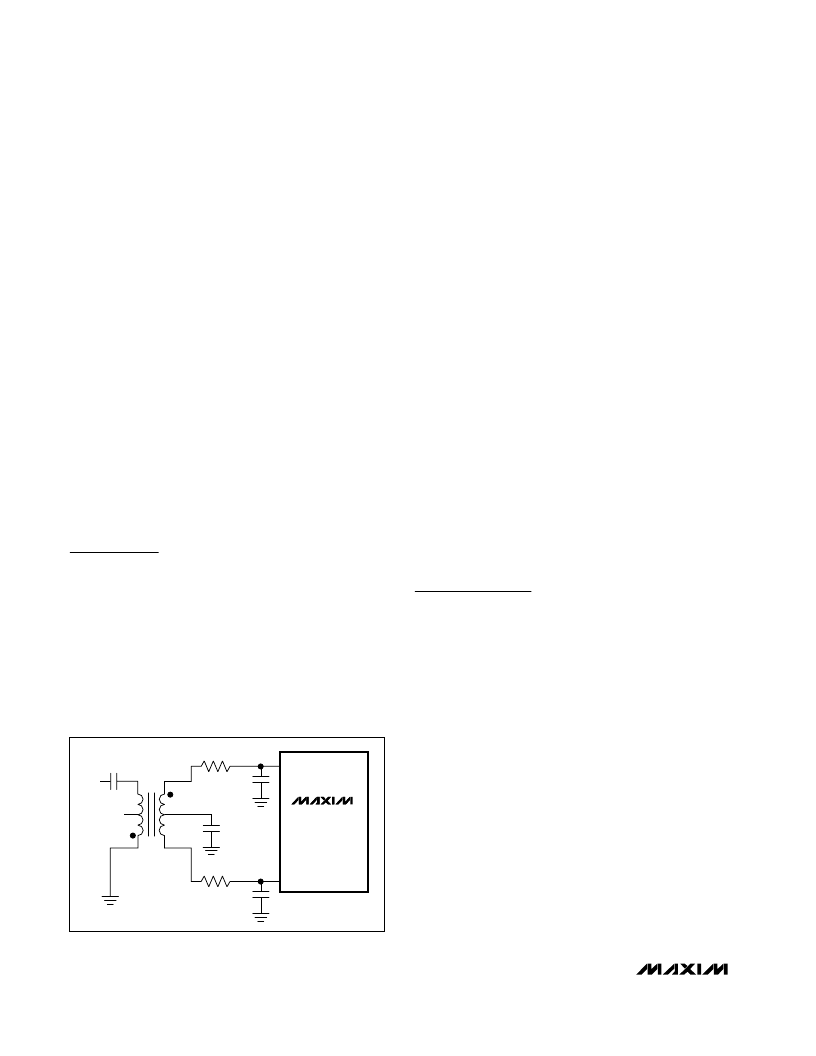

An RF transformer (Figure 9) provides an excellent

solution to convert a single-ended input source signal

to a fully differential signal, required by the MAX1127

for optimum performance. The MAX1127 input com-

mon-mode voltage is internally biased to 0.6V (typ) with

f

CLK

= 65MHz. Although a 1:1 transformer is shown, a

step-up transformer can be selected to reduce the

drive requirements. A reduced signal swing from the

input driver, such as an op amp, can also improve the

overall distortion.

Grounding, Bypassing, and Board Layout

The MAX1127 requires high-speed board layout design

techniques. Refer to the MAX1127 EV kit data sheet for

a board layout reference. Locate all bypass capacitors

as close to the device as possible, preferably on the

same side as the ADC, using surface-mount devices

for minimum inductance. Bypass AV

DD

to GND with a

0.1μF ceramic capacitor in parallel with a

≥

2.2μF

ceramic capacitor. Bypass OV

DD

to GND with a 0.1μF

ceramic capacitor in parallel with a

≥

2.2μF ceramic

capacitor. Bypass CV

DD

to GND with a 0.1μF ceramic

capacitor in parallel with a

≥

2.2μF ceramic capacitor.

Multilayer boards with ample ground and power planes

produce the highest level of signal integrity. Connect

MAX1127 ground pins and the exposed backside pad-

dle to the same ground plane. The MAX1127 relies on

the exposed backside paddle connection for a low-

inductance ground connection. Isolate the ground

plane from any noisy digital system ground planes.

Route high-speed digital signal traces away from the

sensitive analog traces. Keep all signal lines short and

free of 90° turns.

Ensure that the differential analog input network layout

is symmetric and that all parasitics are balanced equal-

ly. Refer to the MAX1127 EV kit data sheet for an exam-

ple of symmetric input layout.

Parameter Definitions

Integral Nonlinearity (INL)

Integral nonlinearity is the deviation of the values on an

actual transfer function from a straight line. For the

MAX1127, this straight line is between the end points of

the transfer function, once offset and gain errors have

been nullified. INL deviations are measured at every

step and the worst-case deviation is reported in the

Electrical Characteristics

table.

Differential Nonlinearity (DNL)

Differential nonlinearity is the difference between an

actual step width and the ideal value of 1 LSB. A DNL

error specification of less than 1 LSB guarantees no

missing codes and a monotonic transfer function. For

the MAX1127, DNL deviations are measured at every

step and the worst-case deviation is reported in the

Electrical Characteristics

table.

Offset Error

Offset error is a figure of merit that indicates how well

the actual transfer function matches the ideal transfer

function at a single point. For the MAX1127, the ideal

midscale digital output transition occurs when there is

-1/2 LSB across the analog inputs (Figures 6 and 7).

MAX1127

V

IN

0.1

μ

F

0.1

μ

F

N.C.

1

2

3

MINICIRCUITS

ADT1-1WT

6

5

4

T1

10

10

39pF

39pF

IN_P

IN_N

Figure 9. Transformer-Coupled Input Drive

相关PDF资料 |

PDF描述 |

|---|---|

| MAX1134 | Low-Voltage Adjustable Precision Shunt Regulator 3-SOT-23 0 to 70 |

| MAX1134BCAP | Low-Voltage Adjustable Precision Shunt Regulator 3-SOT-23 0 to 70 |

| MAX1134BEAP | Low-Voltage Adjustable Precision Shunt Regulator 3-SOT-89 0 to 70 |

| MAX1135BCAP | Low-Voltage Adjustable Precision Shunt Regulator 3-SOT-89 0 to 70 |

| MAX1135BEAP | 16-Bit ADCs, 150ksps, 3.3V Single Supply |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX1127EGK+D | 制造商:Maxim Integrated Products 功能描述:ADC QUAD PIPELINED 65MSPS 12-BIT SERL 68QFN - Bulk |

| MAX1127EGK+TD | 制造商:Maxim Integrated Products 功能描述:ADC QUAD PIPELINED 65MSPS 12-BIT SERL 68QFN - Tape and Reel |

| MAX1127EVKIT | 制造商:Maxim Integrated Products 功能描述:QUAD 65MSPS 12-BIT ADC WITH SERIAL LVDS - Bulk |

| MAX113 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:4-Digit.Up/Down Counter Decoder Driver[MM74C945/MM74C947/MM74C945C/D/MM74C945N ] |

| MAX1132 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:16-Bit ADC, 200ksps, 5V Single-Supply with Reference |

发布紧急采购,3分钟左右您将得到回复。