- 您现在的位置:买卖IC网 > PDF目录17021 > MAX1162EVC16 (Maxim Integrated Products)EVAL KIT FOR MAX1162 PDF资料下载

参数资料

| 型号: | MAX1162EVC16 |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 4/18页 |

| 文件大小: | 0K |

| 描述: | EVAL KIT FOR MAX1162 |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 1 |

| ADC 的数量: | 1 |

| 位数: | 16 |

| 采样率(每秒): | 200k |

| 数据接口: | 串行 |

| 输入范围: | 0 ~ VREF |

| 工作温度: | 0°C ~ 70°C |

| 已用 IC / 零件: | MAX1162,MAX1062 |

| 已供物品: | 2 板,CD |

MAX1162

16-Bit, +5V, 200ksps ADC with 10A

Shutdown

12

______________________________________________________________________________________

quency band of interest. Minimize noise by presenting

a low impedance (at the frequencies contained in the

noise signal) at the inputs. This requires bypassing AIN

to AGND, or buffering the input with an amplifier that

has a small-signal bandwidth of several MHz, or prefer-

ably both. AIN has 4MHz (typ) of bandwidth.

Distortion

Avoid degrading dynamic performance by choosing an

amplifier with distortion much less than the MAX1162’s

total harmonic distortion (THD = -102dB at 1kHz) at fre-

quencies of interest. If the chosen amplifier has insuffi-

cient common-mode rejection, which results in degraded

THD performance, use the inverting configuration (posi-

tive input grounded) to eliminate errors from this source.

Low temperature-coefficient, gain-setting resistors reduce

linearity errors caused by resistance changes due to self-

heating. To reduce linearity errors due to finite amplifier

gain, use amplifier circuits with sufficient loop gain at the

frequencies of interest.

DC Accuracy

To improve DC accuracy, choose a buffer with an offset

much less than the MAX1162’s offset (1mV (max) for +5V

supply), or whose offset can be trimmed while maintain-

ing stability over the required temperature range.

Serial Interfaces

The MAX1162’s interface is fully compatible with SPI,

QSPI, and MICROWIRE standard serial interfaces.

If a serial interface is available, establish the CPU’s ser-

ial interface as master, so that the CPU generates the

serial clock for the MAX1162. Select a clock frequency

between 100kHz and 4.8MHz:

1) Use a general-purpose I/O line on the CPU to pull

CS low.

2) Activate SCLK for a minimum of 24 clock cycles.

The serial data stream of eight leading zeros fol-

lowed by the MSB of the conversion result begins at

the falling edge of CS. DOUT transitions on SCLK’s

falling edge and the output is available in MSB-first

A0

A1

CLK

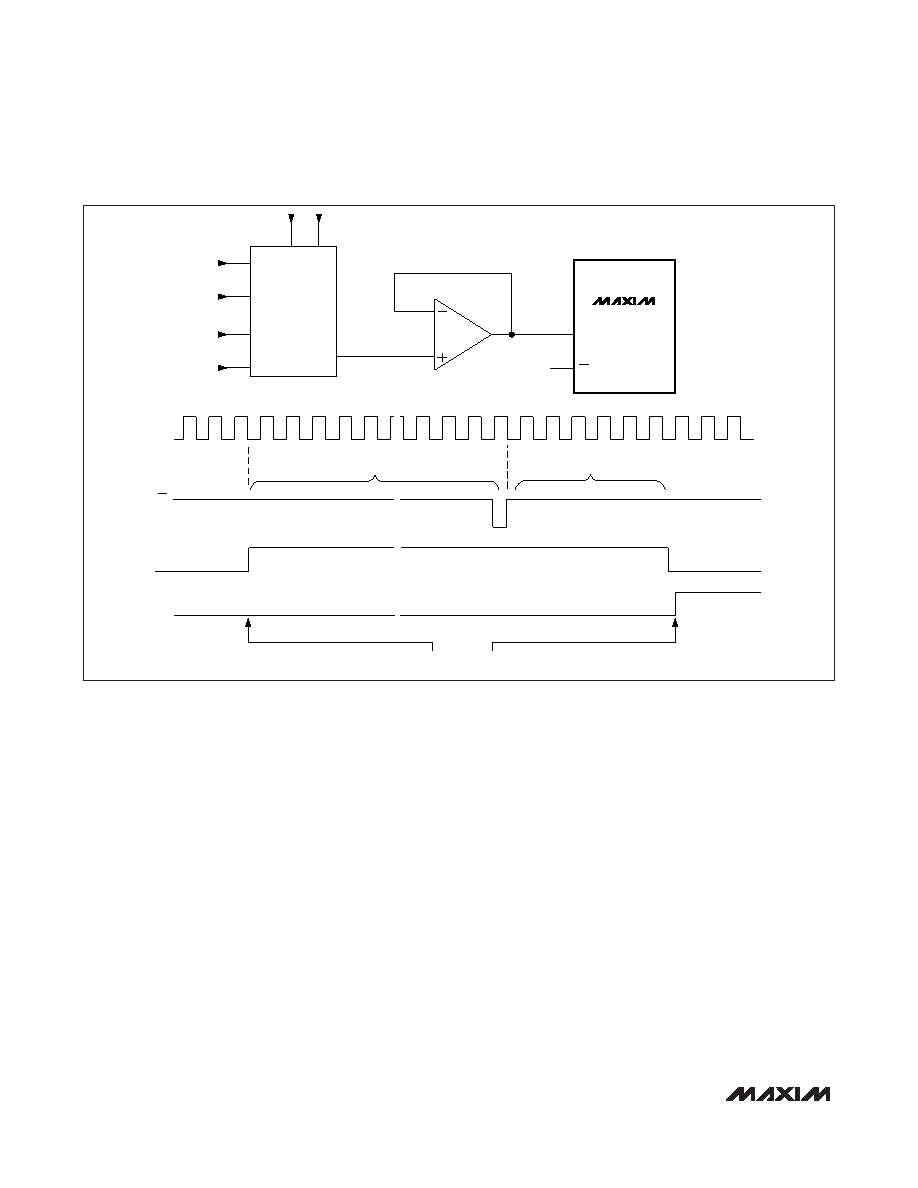

CHANGE MUX INPUT HERE

CONVERSION

IN1

A0

A1

IN2

IN3

IN4

OUT

ACQUISITION

4-TO-1

MUX

AIN

CS

MAX1162

CS

TIMING NOT TO SCALE.

Figure 9. Change Multiplexer Input Near Beginning of Conversion to Allow Time for Slewing and Settling

相关PDF资料 |

PDF描述 |

|---|---|

| MAX11617EVSYS+ | EVALUATION SYSTEM FOR MAX11617 |

| LLS1J472MELB | CAP ALUM 4700UF 63V 20% SNAP |

| LGU2G151MELA | CAP ALUM 150UF 400V 20% SNAP |

| VE-B5W-EY | CONVERTER MOD DC/DC 5.5V 50W |

| MAX11616EVSYS+ | EVALUATION SYSTEM FOR MAX11616 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX1162EVKIT | 功能描述:数据转换 IC 开发工具 MAX1162/1062 Eval Kit RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| MAX1162EVSYS | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Evaluation System/Evaluation Kit for the MAX1162/MAX1062 |

| MAX11630EEG+ | 制造商:Maxim Integrated Products 功能描述:12-BIT 300KSPS ADCS WITH FIFO AND INTERNAL REFERENCE - Rail/Tube |

| MAX11630EEG+T | 制造商:Maxim Integrated Products 功能描述:12-BIT 300KSPS ADCS WITH FIFO AND INTERNAL REFERENCE - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。