- 您现在的位置:买卖IC网 > PDF目录17021 > MAX1162EVC16 (Maxim Integrated Products)EVAL KIT FOR MAX1162 PDF资料下载

参数资料

| 型号: | MAX1162EVC16 |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 7/18页 |

| 文件大小: | 0K |

| 描述: | EVAL KIT FOR MAX1162 |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 1 |

| ADC 的数量: | 1 |

| 位数: | 16 |

| 采样率(每秒): | 200k |

| 数据接口: | 串行 |

| 输入范围: | 0 ~ VREF |

| 工作温度: | 0°C ~ 70°C |

| 已用 IC / 零件: | MAX1162,MAX1062 |

| 已供物品: | 2 板,CD |

MAX1162

16-Bit, +5V, 200ksps ADC with 10A

Shutdown

______________________________________________________________________________________

15

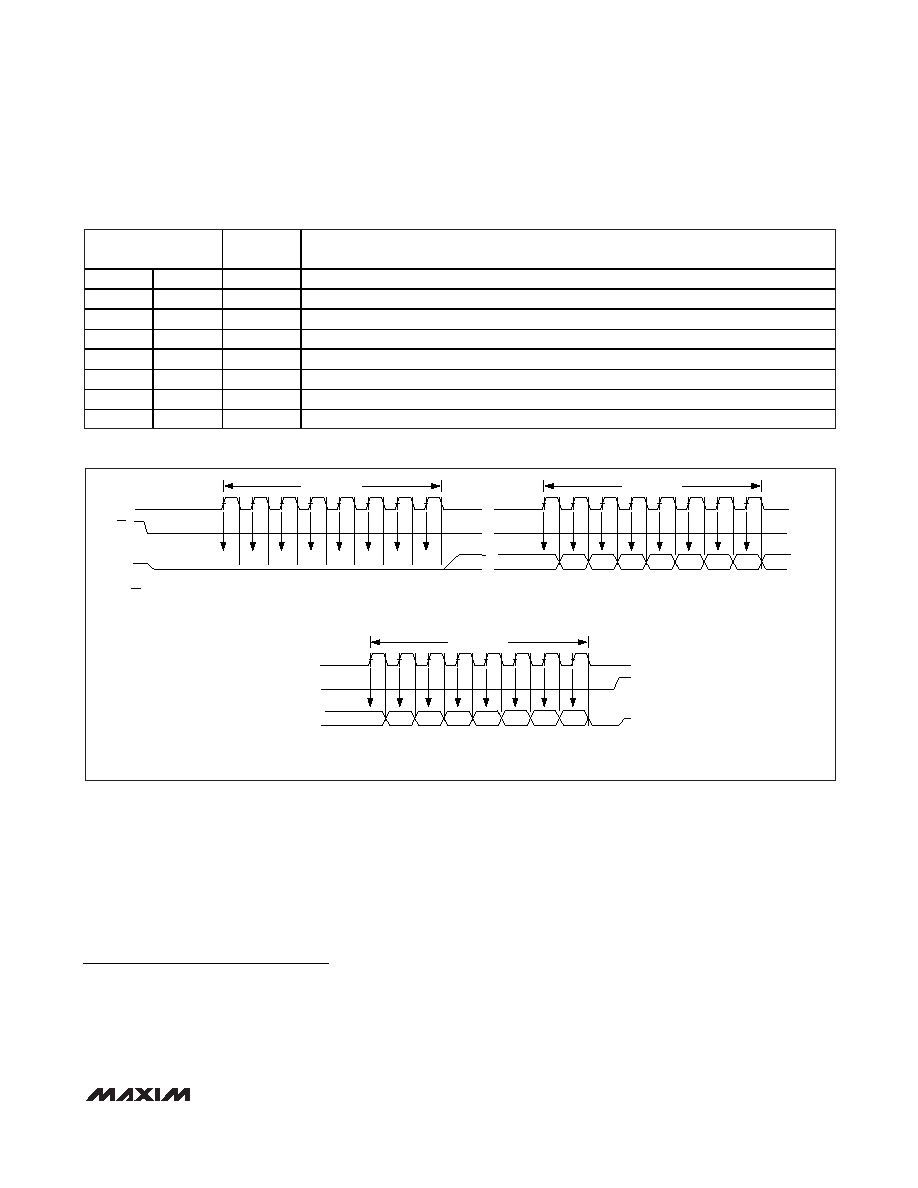

neously. Three consecutive 8-bit readings (Figure 12b)

are necessary to obtain the entire 16-bit result from the

ADC. DOUT data transitions on the serial clock’s falling

edge and is clocked into the C on SCLK’s rising edge.

The first 8-bit data stream contains all zeros. The sec-

ond 8-bit data stream contains the MSB through D8.

The third 8-bit data stream contains bits D7 through D0.

Definitions

Integral Nonlinearity

Integral nonlinearity (INL) is the deviation of the values

on an actual transfer function from a straight line. This

straight line can be either a best-fit straight line fit or a

line drawn between the endpoints of the transfer func-

tion, once offset and gain errors have been nulled. The

static linearity parameters for the MAX1162 are mea-

sured using the endpoint method.

Differential Nonlinearity

Differential nonlinearity (DNL) is the difference between

an actual step width and the ideal value of 1LSB. A

DNL error specification of 1LSB guarantees no missing

codes and a monotonic transfer function.

Aperture Definitions

Aperture jitter (tAJ) is the sample-to-sample variation in

the time between samples. Aperture delay (tAD) is the

time between the falling edge of the sampling clock

and the instant when the actual sample is taken.

CONTROL BIT

MAX1162

SETTINGS

SYNCHRONOUS SERIAL-PORT CONTROL REGISTER (SSPSTAT)

SMP

BIT7

0

SPI Data Input Sample Phase. Input data is sampled at the middle of the data output time.

CKE

BIT6

1

SPI Clock Edge Select Bit. Data is transmitted on the rising edge of the serial clock.

D/A

BIT5

X

Data Address Bit

P

BIT4

X

Stop Bit

S

BIT3

X

Start Bit

R/W

BIT2

X

Read/Write Bit Information

UA

BIT1

X

Update Address

BF

BIT0

X

Buffer Full Status Bit

Table 2. Detailed SSPSTAT Register Contents

DOUT*

CS

SCLK

1ST BYTE READ

2ND BYTE READ

*WHEN CS IS HIGH, DOUT = HIGH-Z

MSB

HIGH-Z

3RD BYTE READ

LSB

D1

D0

D7

D6

D5

D4

D3

D2

24

20

16

12

D15

D14

D13

D12

D11

D10

D9

D8

0

00

0

D7

TIMING NOT TO SCALE.

Figure 12b. SPI Interface Timing with PIC16/PIC17 in Master Mode (CKE = 1, CKP = 0, SMP = 0, SSPM3 - SSPM0 = 0001)

X = Don’t care.

相关PDF资料 |

PDF描述 |

|---|---|

| MAX11617EVSYS+ | EVALUATION SYSTEM FOR MAX11617 |

| LLS1J472MELB | CAP ALUM 4700UF 63V 20% SNAP |

| LGU2G151MELA | CAP ALUM 150UF 400V 20% SNAP |

| VE-B5W-EY | CONVERTER MOD DC/DC 5.5V 50W |

| MAX11616EVSYS+ | EVALUATION SYSTEM FOR MAX11616 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX1162EVKIT | 功能描述:数据转换 IC 开发工具 MAX1162/1062 Eval Kit RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| MAX1162EVSYS | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Evaluation System/Evaluation Kit for the MAX1162/MAX1062 |

| MAX11630EEG+ | 制造商:Maxim Integrated Products 功能描述:12-BIT 300KSPS ADCS WITH FIFO AND INTERNAL REFERENCE - Rail/Tube |

| MAX11630EEG+T | 制造商:Maxim Integrated Products 功能描述:12-BIT 300KSPS ADCS WITH FIFO AND INTERNAL REFERENCE - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。