- 您现在的位置:买卖IC网 > PDF目录9944 > MAX11632EEG+ (Maxim Integrated Products)ADC 12BIT 300KSPS 16CH 24-QSOP PDF资料下载

参数资料

| 型号: | MAX11632EEG+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 5/22页 |

| 文件大小: | 0K |

| 描述: | ADC 12BIT 300KSPS 16CH 24-QSOP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 50 |

| 位数: | 12 |

| 采样率(每秒): | 300k |

| 数据接口: | MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 1 |

| 功率耗散(最大): | 762mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-SSOP(0.154",3.90mm 宽) |

| 供应商设备封装: | 24-QSOP |

| 包装: | 管件 |

| 输入数目和类型: | 16 个单端,单极 |

MAX11626–MAX11629/MAX11632/MAX11633

12-Bit, 300ksps ADCs

with FIFO and Internal Reference

______________________________________________________________________________________

13

True Differential Analog Input T/H

The equivalent circuit of Figure 3 shows the

MAX11626–MAX11629/MAX11632/MAX11633’s input

architecture. In track mode, a positive input capacitor is

connected to AIN0–AIN15. A negative input capacitor is

connected to GND. For external T/H timing, use clock

mode 01. After the T/H enters hold mode, the difference

between the sampled positive and negative input volt-

ages is converted. The time required for the T/H to

acquire an input signal is determined by how quickly its

input capacitance is charged. If the input signal’s

source impedance is high, the required acquisition time

lengthens. The acquisition time, tACQ, is the maximum

time needed for a signal to be acquired, plus the power-

up time. It is calculated by the following equation:

tACQ = 9 x (RS + RIN) x 24pF + tPWR

where RIN = 1.5k, RS is the source impedance of the

input signal, and tPWR = 1s, the power-up time of the

device. The varying power-up times are detailed in the

explanation of the clock mode conversions. When the

conversion is internally timed, tACQ is never less than

1.4s, and any source impedance below 300

does not

significantly affect the ADC’s AC performance. A high-

impedance source can be accommodated either by

lengthening tACQ or by placing a 1F capacitor between

the positive and negative analog inputs.

Internal FIFO

The MAX11626–MAX11629/MAX11632/MAX11633 con-

tain a FIFO buffer that can hold up to 16 ADC results.

This allows the ADC to handle multiple internally clocked

conversions, without tying up the serial bus. If the FIFO is

filled and further conversions are requested without

reading from the FIFO, the oldest ADC results are over-

written by the new ADC results. Each result contains 2

bytes, with the MSB preceded by four leading zeros.

After each falling edge of CS, the oldest available byte of

data is available at DOUT, MSB first. When the FIFO is

empty, DOUT is zero.

Internal Clock

The MAX11626–MAX11629/MAX11632/MAX11633 oper-

ate from an internal oscillator, which is accurate within

10% of the 4.4MHz nominal clock rate. The internal

oscillator is active in clock modes 00, 01, and 10. Read

out the data at clock speeds up to 10MHz. See Figures

4–7 for details on timing specifications and starting a

conversion.

Applications Information

Register Descriptions

The MAX11626–MAX11629/MAX11632/MAX11633 com-

municate between the internal registers and the exter-

nal circuitry through the SPI-/QSPI-compatible serial

interface. Table 1 details the registers and the bit

names. Tables 2–5 show the various functions within

the conversion register, setup register, averaging regis-

ter, and reset register.

Conversion Time Calculations

The conversion time for each scan is based on a num-

ber of different factors: conversion time per sample,

samples per result, results per scan, and if the external

reference is in use.

Use the following formula to calculate the total conver-

sion time for an internally timed conversion in clock

modes 00 and 10 (see the

Electrical Characteristics

section as applicable):

Total Conversion Time = tCNV x nAVG x nRESULT + tRP

where

tCNV = tACQ (max) + tCONV (max).

nAVG = samples per result (amount of averaging).

nRESULT = number of FIFO results requested;

determined by the number of channels being

scanned or by NSCAN1, NSCAN0.

tRP = internal reference wake-up; set to zero if inter-

nal reference is already powered up or external ref-

erence is being used .

In clock mode 01, the total conversion time depends on

how long CNVST is held low or high, including any time

required to turn on the internal reference. Conversion

time in externally clocked mode (CKSEL1, CKSEL0 = 11)

depends on the SCLK period and how long CS is held

high between each set of eight SCLK cycles. In clock

mode 01, the total conversion time does not include the

time required to turn on the internal reference.

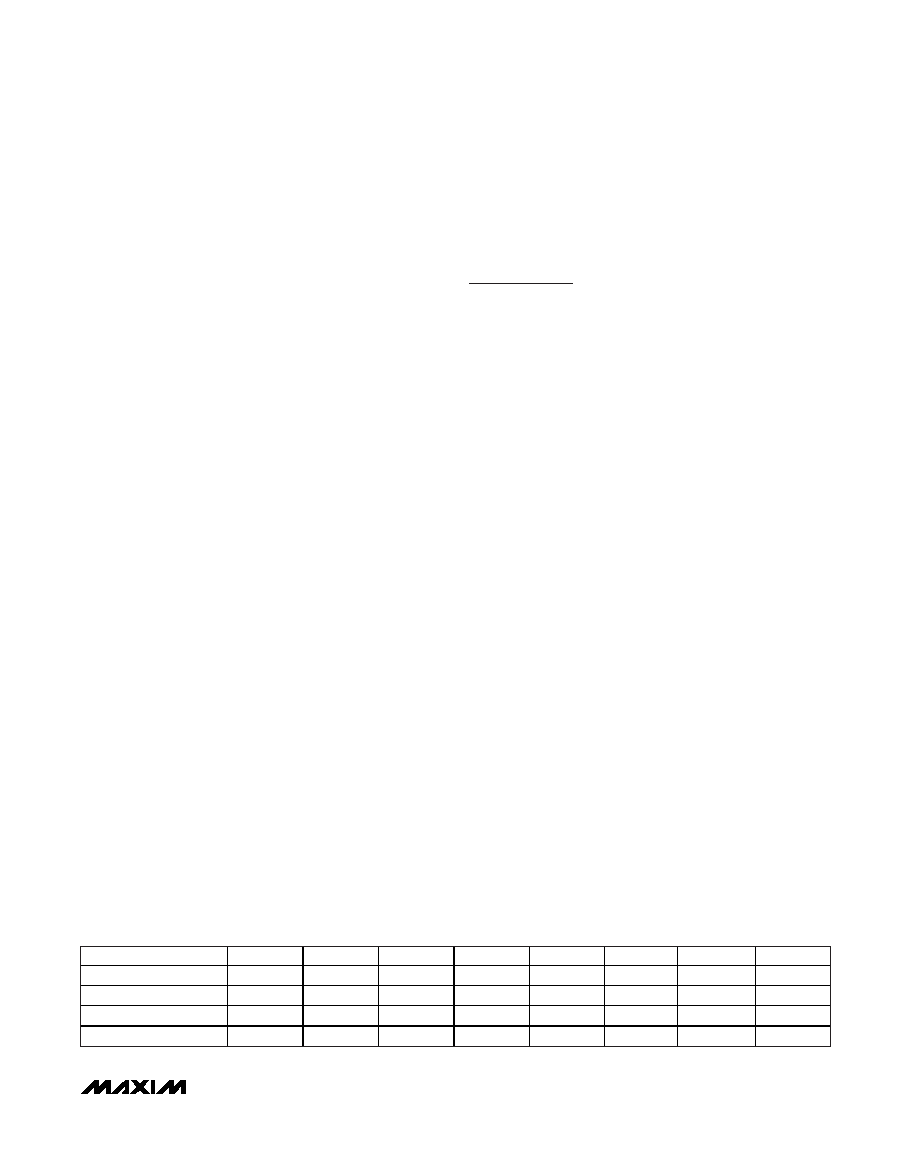

REGISTER NAME

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

Conversion

1

CHSEL3

CHSEL2

CHSEL1

CHSEL0

SCAN1

SCAN0

X

Setup

0

1

CKSEL1

CKSEL0

REFSEL1

REFSEL0

X

Averaging

0

1

AVGON

NAVG1

NAVG0

NSCAN1

NSCAN0

Reset

0001

RESET

XX

X

Table 1. Input Data Byte (MSB First)

X = Don’t care.

相关PDF资料 |

PDF描述 |

|---|---|

| VE-21W-CU-B1 | CONVERTER MOD DC/DC 5.5V 200W |

| MS27467T11B35S EDR | CONN PLUG 13POS STRAIGHT W/SCKT |

| IDT72291L15TF8 | IC FIFO 65536X18 LP 15NS 64QFP |

| VI-21W-CU-B1 | CONVERTER MOD DC/DC 5.5V 200W |

| ISL3156EIBZ-T | TXRX ESD 5V RS-485/422 14-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX11632EEG+ | 功能描述:模数转换器 - ADC 12-Bit 16Ch 300ksps 5.25V Precision ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX11632EEG+T | 功能描述:模数转换器 - ADC 12-Bit 16Ch 300ksps 5.25V Precision ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX11633 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:12-Bit, 300ksps ADCs with FIFO and Internal Reference |

| MAX11633EEG | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:12-Bit, 300ksps ADCs with FIFO and Internal Reference |

| MAX11633EEG+ | 功能描述:模数转换器 - ADC 12-Bit 16Ch 300ksps 3.6V Precision ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

发布紧急采购,3分钟左右您将得到回复。