- 您现在的位置:买卖IC网 > PDF目录383311 > MAX1168ACEG (MAXIM INTEGRATED PRODUCTS INC) Multichannel, 16-Bit, 200ksps Analog-to-Digital Converters PDF资料下载

参数资料

| 型号: | MAX1168ACEG |

| 厂商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分类: | ADC |

| 英文描述: | Multichannel, 16-Bit, 200ksps Analog-to-Digital Converters |

| 中文描述: | 8-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO24 |

| 封装: | 0.150 INCH, 0.025 INCH PITCH, MO-137AE, QSOP-24 |

| 文件页数: | 6/30页 |

| 文件大小: | 462K |

| 代理商: | MAX1168ACEG |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页

M

Multichannel, 16-Bit, 200ksps Analog-to-Digital

Converters

6

_______________________________________________________________________________________

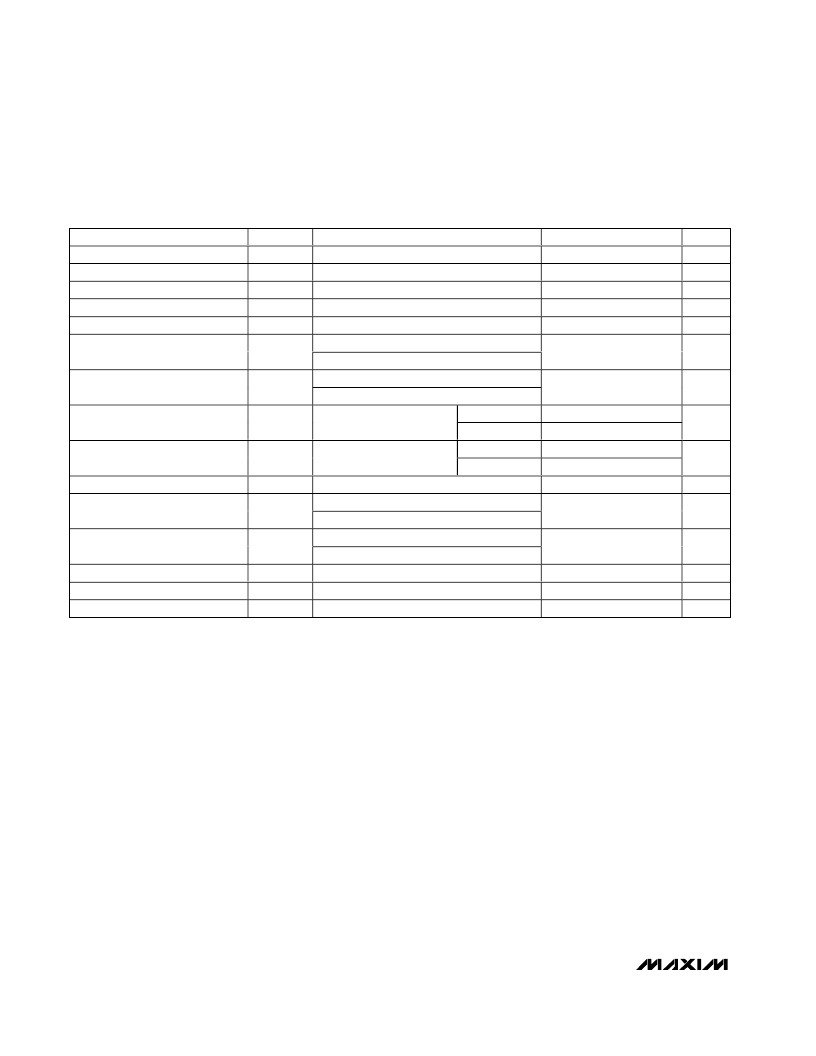

TIMING CHARACTERISTICS (Figures 1, 2, 8, and 16)

(AV

DD

= +4.75V to +5.25V,

DV

DD

= +2.7V to +5.25V

, f

SCLK

= 4.8MHz external clock (50% duty cycle), 24 clocks/conversion

(200ksps), external V

REF

= +4.096V, T

A

= T

MIN

to T

MAX

, unless otherwise noted. Typical values are at T

A

= +25

°

C.)

PARAMETER

SYMBOL

CONDITIONS

Acquisition Time

t

ACQ

External clock (Note 6)

SCLK to DOUT Valid

t

DO

C

DOUT

= 30pF

CS

Fall to DOUT Enable

t

DV

C

DOUT

= 30pF

CS

Rise to DOUT Disable

t

TR

C

DOUT

= 30pF

CS

Pulse Width

t

CSW

SCLK rise

CS

to SCLK Setup

t

CSS

SCLK fall (DSP)

SCLK rise

CS

to SCLK Hold

t

CSH

SCLK fall (DSP)

MIN

729

TYP

MAX

UNITS

ns

ns

ns

ns

ns

100

100

80

100

100

ns

0

ns

Conversion

Data transfer

Conversion

Data transfer

93

93

93

93

209

SCLK High Pulse Width

t

CH

Duty cycle 45% to 55%

ns

SCLK Low Pulse Width

t

CL

Duty cycle 45% to 55%

ns

SCLK Period

t

CP

ns

SCLK rise

SCLK fall (DSP)

SCLK rise

SCLK fall (DSP)

DIN to SCLK Setup

t

DS

100

ns

DIN to SCLK Hold

t

DH

0

ns

CS

Falling to DSPR Rising

DSPR to SCLK Falling Setup

DSPR to SCLK Falling Hold

t

DF

t

FSS

t

FSH

100

100

0

ns

ns

ns

Note 1:

AV

DD

= DV

DD

= +5.0V.

Note 2:

Relative accuracy is the deviation of the analog value at any code from its theoretical value after full-scale range has been

calibrated.

Note 3:

Offset and reference errors nulled.

Note 4:

DC voltage applied to on channel, and a full-scale 1kHz sine wave applied to off channels.

Note 5:

Conversion time is measured from the rising edge of the 8th external SCLK pulse to

EOC

transition minus t

ACQ

in 8-bit data-

transfer mode.

Note 6:

See Figures 10 and 17.

Note 7:

f

SCLK

= 4.8MHz, f

INTCLK

= 4.0MHz. Sample rate is calculated with the formula f

s

= n

1

(n

2

/ f

SCLK

+ n

3

/ f

INTCLK

)-1where: n

1

= number of scans, n

2

= number of SCLK cycles, and n

3

= number of internal clock cycles (see Figures 11

–

14).

Note 8:

Internal reference and buffer are left on between conversions.

Note 9:

Defined as the change in the positive full scale caused by a ±5% variation in the nominal supply voltage.

相关PDF资料 |

PDF描述 |

|---|---|

| MAX1168BCEG | Multichannel, 16-Bit, 200ksps Analog-to-Digital Converters |

| MAX1167BEEE | Multichannel, 16-Bit, 200ksps Analog-to-Digital Converters |

| MAX1167CCEE | Multichannel, 16-Bit, 200ksps Analog-to-Digital Converters |

| MAX1167CEEE | Multichannel, 16-Bit, 200ksps Analog-to-Digital Converters |

| MAX1168BEEG | Multichannel, 16-Bit, 200ksps Analog-to-Digital Converters |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX1168ACEG+ | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX1168ACEG+T | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX1168ACEG-T | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX1168AEEG | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX1168AEEG+ | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

发布紧急采购,3分钟左右您将得到回复。