- 您现在的位置:买卖IC网 > PDF目录2088 > MAX3625ACUG+T (Maxim Integrated Products)IC CLOCK GENERATOR PREC 24-TSSOP PDF资料下载

参数资料

| 型号: | MAX3625ACUG+T |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 6/10页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GENERATOR PREC 24-TSSOP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 2,500 |

| 类型: | 时钟发生器 |

| PLL: | 带旁路 |

| 输入: | LVCMOS,晶体 |

| 输出: | LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:3 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 318.75MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 24-TSSOP |

| 包装: | 带卷 (TR) |

MAX3625A

Low-Jitter, Precision Clock

Generator with Three Outputs

_______________________________________________________________________________________

5

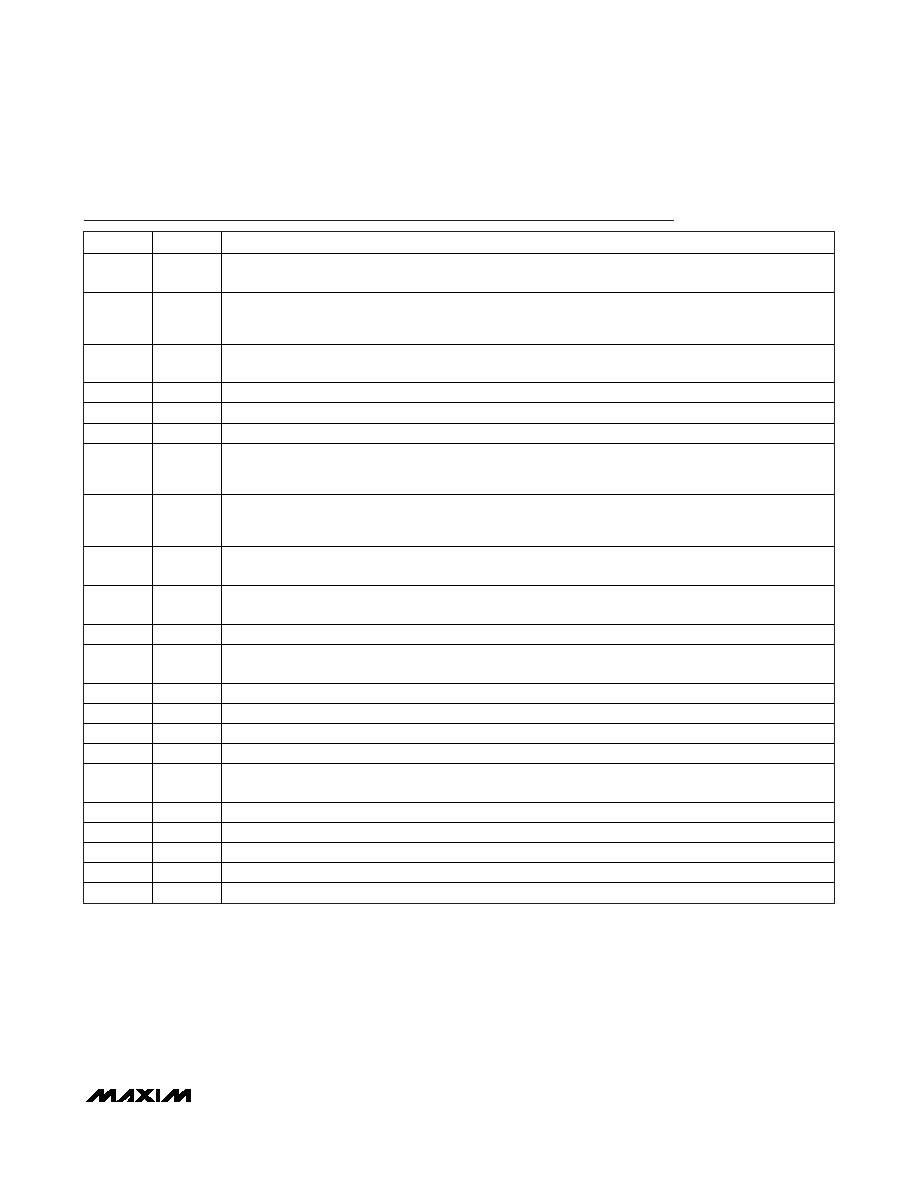

Pin Description

PIN

NAME

FUNCTION

1, 24

SELB0,

SELB1

LVCMOS/LVTTL Inputs. Control NB divider setting. Has 50k

input impedance. See Table 2 for more

information.

2

BYPASS

LVCMOS/LVTTL Input (Active Low). Connect low to bypass the internal PLL. Connect high or leave

open for normal operation. When in bypass mode the output dividers are set to divide by 1. Has

internal 75k

pullup to VCC.

3

MR

LVCMOS/LVTTL Input. Master reset input. Pulse high for > 1μs to reset all dividers. Has internal 75k

pulldown to GND. Not required for normal operation.

4

VCCO_A

Power Supply for QA Clock Output. Connect to +3.3V.

5

QA

Noninverting Clock Output, LVPECL

6

QA

Inverting Clock Output, LVPECL

7

QB_OE

LVCMOS/LVTTL Input. Enables/disables QB clock outputs. Connect pin high or leave open to enable

LVPECL clock outputs QB0 and QB1. Connect low to set QB0 and QB1 to a logic 0. Has internal 75k

pullup to VCC.

8

QA_OE

LVCMOS/LVTTL Input. Enables/disables the QA clock output. Connect this pin high or leave open to

enable the LVPECL clock output QA. Connect low to set QA to a logic 0. Has internal 75k

pullup to

VCC.

9

FB_SEL

LVCMOS/LVTTL Input. Controls M divider setting. See Table 3 for more information. Has internal 75k

pulldown to GND.

10

VCCA

Analog Power Supply for the VCO. Connect to +3.3V. For additional power-supply noise filtering, this

pin can connect to VCC through 10.5

as shown in Figure 1 (requires VCC = 3.3V ±5%).

11

VCC

Core Power Supply. Connect to +3.3V.

12, 13

SELA0,

SELA1

LVCMOS/LVTTL Inputs. Control NA divider setting. See Table 2 for more information. 50k

input

impedance.

14

GND

Supply Ground

15

X_OUT

Crystal Oscillator Output

16

X_IN

Crystal Oscillator Input

17

REF_IN

LVCMOS Reference Clock Input. Self-biased to allow AC- or DC-coupling.

18

IN_SEL

LVCMOS/LVTTL Input. Connect high or leave open to use a crystal. Connect low to use REF_IN. Has

internal 75k

pullup to VCC.

19

QB1

LVPECL, Inverting Clock Output

20

QB1

LVPECL, Noninverting Clock Output

21

QB0

LVPECL, Inverting Clock Output

22

QB0

LVPECL, Noninverting Clock Output

23

VCCO_B

Power Supply for QB0 and QB1 Clock Output. Connect to +3.3V.

相关PDF资料 |

PDF描述 |

|---|---|

| MAX3625BEUG+T | IC CLOCK GENERATOR PREC 24TSSOP |

| MAX3645EEE+T | IC AMP LIMITING 16-QSOP |

| MAX3654ETE+T | IC AMP TRANSIMPEDANCE 16-TQFN |

| MAX3658AETA+T | IC AMP TRANSIMPEDANCE 8-TDFN |

| MAX3660ETE+T | IC TRANSIMPEDANCE AMP 16TQFN-EP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX3625BEUG+ | 功能描述:时钟发生器及支持产品 Low Jitter Precision w/Four Outputs RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MAX3625BEUG+T | 功能描述:时钟发生器及支持产品 Low Jitter Precision w/Four Outputs RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MAX3625BEVKIT+ | 功能描述:时钟发生器及支持产品 Not Available From Mouser RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MAX3625CUG+ | 功能描述:时钟发生器及支持产品 Not Available From Mouser RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MAX3625CUG+T | 功能描述:时钟发生器及支持产品 Not Available From Mouser RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

发布紧急采购,3分钟左右您将得到回复。