- 您现在的位置:买卖IC网 > PDF目录2011 > MAX5858AECM+D (Maxim Integrated Products)IC DAC 10BIT DUAL 300MSPS 48TQFP PDF资料下载

参数资料

| 型号: | MAX5858AECM+D |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 13/25页 |

| 文件大小: | 0K |

| 描述: | IC DAC 10BIT DUAL 300MSPS 48TQFP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 250 |

| 设置时间: | 11ns |

| 位数: | 10 |

| 数据接口: | 并联 |

| 转换器数目: | 2 |

| 电压电源: | 单电源 |

| 功率耗散(最大): | 816mW |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-TQFP 裸露焊盘 |

| 供应商设备封装: | 48-TQFP 裸露焊盘(7x7) |

| 包装: | 托盘 |

| 输出数目和类型: | 2 电流,单极 |

| 采样率(每秒): | 300M |

MAX5858A

Dual, 10-Bit, 300Msps, DAC with 4x/2x/1x

Interpolation Filters and PLL

20

______________________________________________________________________________________

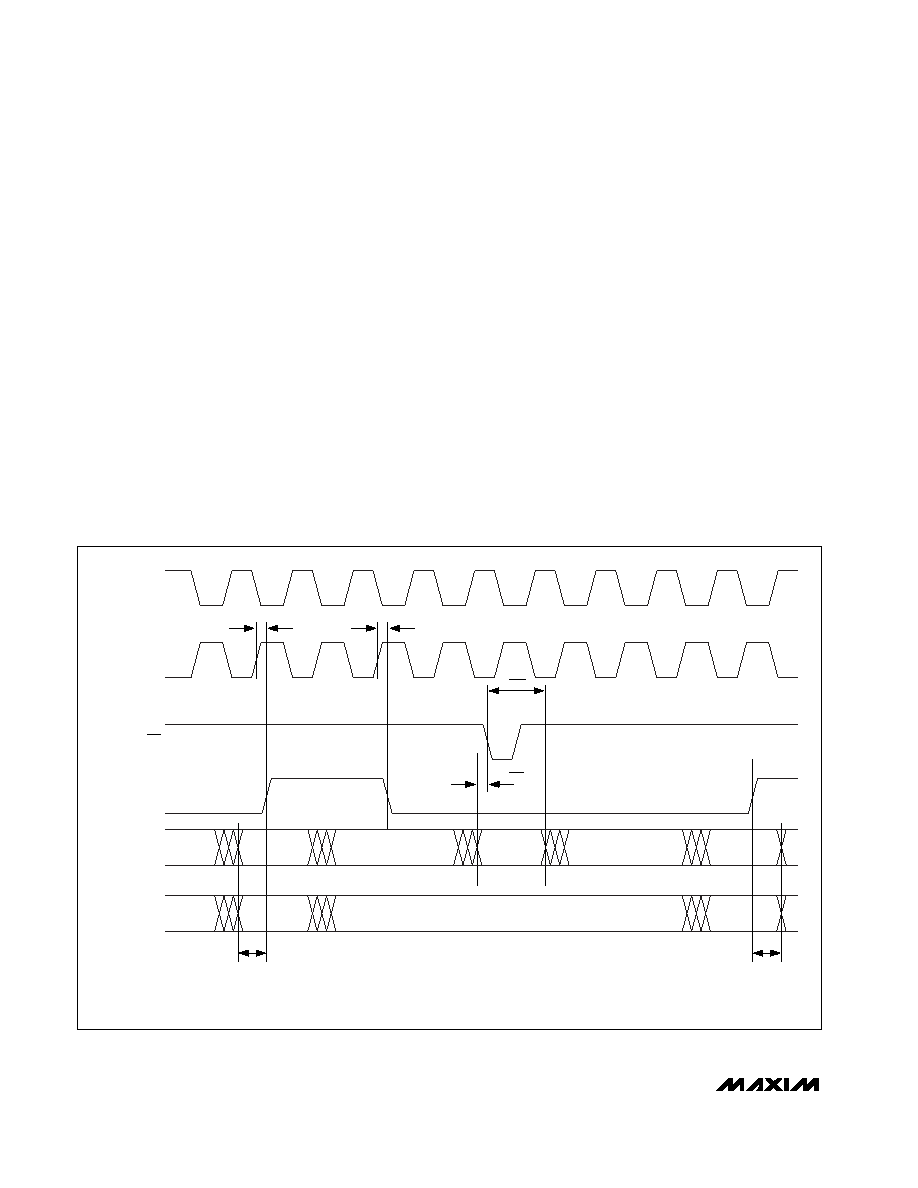

CLKXN

1

CLKXP

1

CLK

2

tCXD

tCWH

tCWS

DA0–DA9/

CONTROL WORD

DB0–DB9

DAN

DAN+1

DBN

DBN+1

CONTROL WORD

tDCSR

tDCHR

1. CLKXP AND CLKXN MUST BE PRESENT WHEN PLL IS DISABLED, WITH PLLEN CONNECTED TO GND. THE DIAGRAM SHOWS 4x INTERPOLATION.

2. CLK IS AN OUTPUT WHEN PLL IS DISABLED WITH PLLEN CONNECTED TO GND, OTHERWISE, IT IS AN INPUT.

CW

Figure 6. Timing Diagram for Noninterleave Data Mode (IDE = Low)

Figure 6 depicts the write cycle of the MAX5858A in 4x

interpolation mode. With the interpolation feature

enabled, the device can operate with the PLL enabled

or disabled.

With the PLL disabled (PLLEN = 0), the clock signal is

applied to CLKXP/CLKXN and internally divided by 4 to

generate the DAC’s CLK signal. The CLK signal is a

divide-by-four output used to synchronize data into the

MAX5858A data ports. The CLKXP/CLKXN signal dri-

ves the interpolation filters and DAC cores at the

desired conversion rate.

If the PLL is enabled (PLLEN = 1), CLK becomes an

input and the clock signal is applied to CLK. In Figure

6, the CLK signal is multiplied by a factor of four by the

PLL and distributed to the interpolation filters and DAC

cores. In this mode, CLKXP must be pulled low and

CLKXN pulled high.

The MAX5858A can operate with a single-ended clock

input used as both data clock and conversion clock. To

operate the device in this mode, disable the interpolation

filters and enable the PLL (PLLEN = 1). Apply a single-

ended clock input at CLK. The CLK signal acts as the

data synchronization clock and DAC core conversion

clock. Though the PLL is enabled, the lock pin (LOCK) is

not valid and the PLL is internally disconnected from

interpolating filters and DAC cores. In this mode, CLKXP

must be pulled low and CLKXN pulled high.

Figure 6 shows the timing for the control word write

pulse (CW). An 8-bit control word routed through chan-

nel A’s data port programs the gain matching, interpo-

lator configuration, and operational mode of the

MAX5858A. The control word is latched on the falling

edge of CW. The CW signal is asynchronous with con-

version clocks CLK and CLKXN/CLKXP; therefore, the

conversion clock (CLK or CLKXN/CLKXP) can run unin-

terrupted when a control word is written to the device.

相关PDF资料 |

PDF描述 |

|---|---|

| MAX5858ECM+D | IC DAC 10BIT DUAL 300MSPS 48TQFP |

| MAX5863ETM+T | IC AFE 8/10BIT 7.5MSPS 48-TQFN |

| MAX5864ETM+T | IC ANLG FRONT END 22MSPS 48-TQFN |

| MAX5865ETM+T | IC ANLG FRONT END 40MSPS 48-TQFN |

| MAX5866ETM+ | IC ANLG FRONT END 60MSPS 48-TQFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX5858AECM-TD | 功能描述:数模转换器- DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| MAX5858AEVKIT | 制造商:Maxim Integrated Products 功能描述:DUAL-10-BIT, 300MSPS, CURRENT-OUTPUT DAC WITH - Bulk |

| MAX5858ECM | 制造商:Rochester Electronics LLC 功能描述: 制造商:Maxim Integrated Products 功能描述: |

| MAX5858ECM+D | 功能描述:数模转换器- DAC 10-Bit 2Ch 300Msps DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| MAX5858ECM+TD | 功能描述:数模转换器- DAC 10-Bit 2Ch 300Msps DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。