- 您现在的位置:买卖IC网 > PDF目录16041 > MAX6750KA29+T (Maxim Integrated Products)IC MPU/RESET CIRC SOT23-8 PDF资料下载

参数资料

| 型号: | MAX6750KA29+T |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 9/14页 |

| 文件大小: | 0K |

| 描述: | IC MPU/RESET CIRC SOT23-8 |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 1 |

| 类型: | 多压监控器 |

| 监视电压数目: | 2 |

| 输出: | 推挽式,图腾柱 |

| 复位: | 低有效 |

| 复位超时: | 可调节/可选择 |

| 电压 - 阀值: | 2.925V,可调 |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | SOT-23-8 |

| 供应商设备封装: | SOT-23-8 |

| 包装: | 标准包装 |

| 产品目录页面: | 1418 (CN2011-ZH PDF) |

| 其它名称: | MAX6750KA29+TDKR |

�� �

�

�

�MAX6746–MAX6753r�

�μP� Reset� Circuits� with� Capacitor-Adjustable�

�Reset/Watchdog� Timeout� Delay�

�V� CC�

�WDI�

�OV�

�V� CC�

�RESET�

�OV�

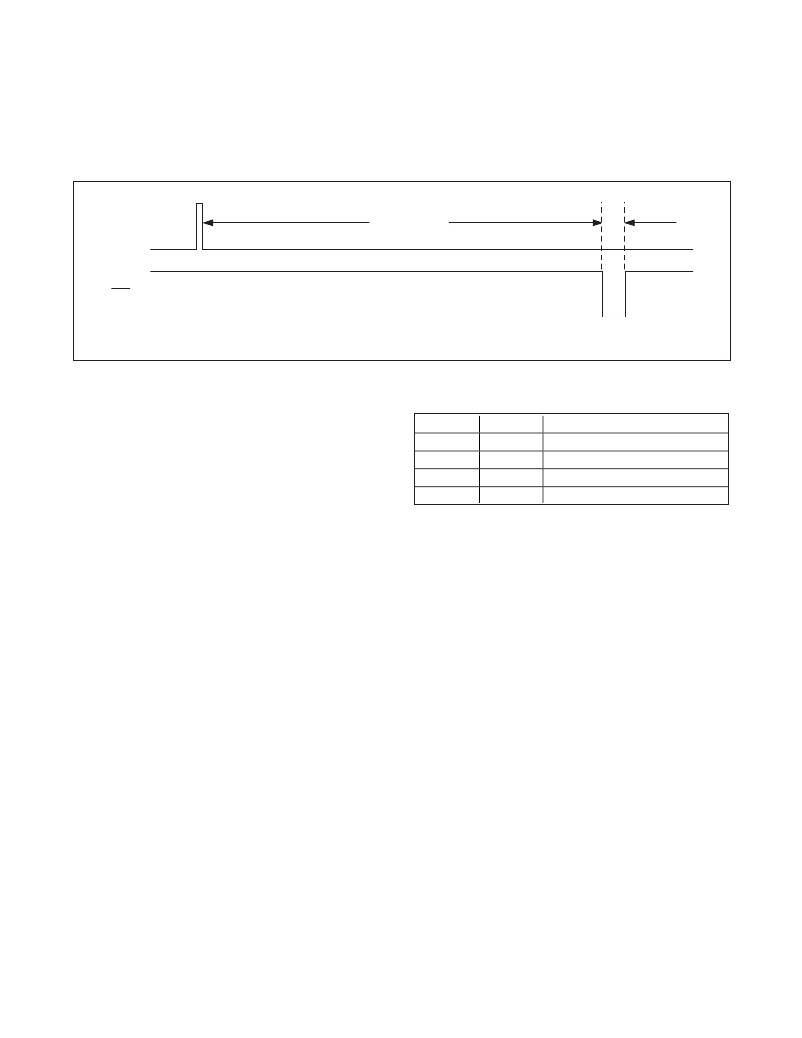

�EXTENDED� MODE� (WDS� =� V� CC� )�

�Figure� 4b.� Watchdog� Timing� Diagram,� WDS� =� V� CC�

�Watchdog� Timer�

�t� WD� x� 128�

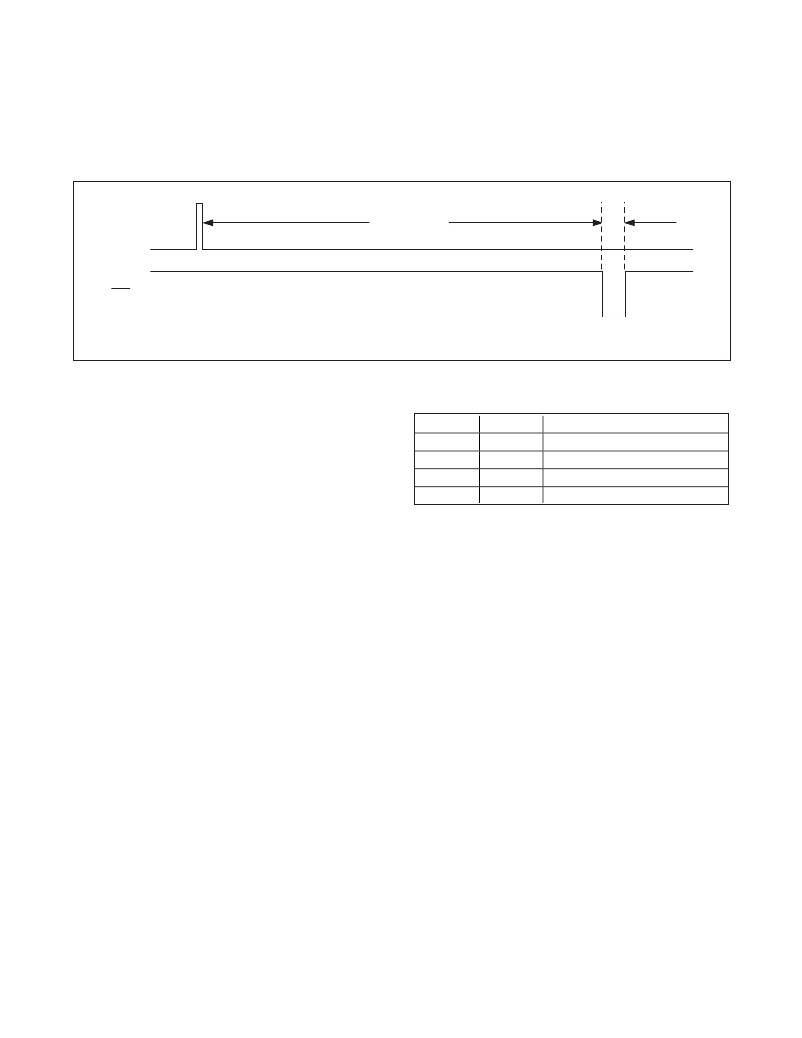

�Table� 1.� Min/Max� Watchdog� Setting�

�t� RP�

�MAX6746–MAX6751�

�The� watchdog’s� circuit� monitors� the� μP’s� activity.� It� the�

�μP� does� not� toggle� the� watchdog� input� (WDI)� within�

�t� WD� (user-selected),� RESET� asserts� for� the� reset� time-�

�out� period.� The� internal� watchdog� timer� is� cleared� by�

�any� event� that� asserts� RESET� ,� by� a� falling� transition� at�

�WDI� (which� can� detect� pulses� as� short� as� 300ns)� or� by�

�SET0�

�LOW�

�LOW�

�HIGH�

�HIGH�

�SET1�

�LOW�

�HIGH�

�LOW�

�HIGH�

�RATIO�

�8�

�16�

�Watchdog� Disabled�

�64�

�a� transition� at� WDS.� The� watchdog� timer� remains�

�cleared� while� reset� is� asserted;� as� soon� as� reset� is�

�released,� the� timer� starts� counting.�

�The� MAX6746–MAX6751� feature� two� modes� of� watch-�

�dog� operation:� normal� mode� and� extended� mode.� In� nor-�

�mal� mode� (Figure� 4a),� the� watchdog� timeout� period� is�

�determined� by� the� value� of� the� capacitor� connected�

�between� SWT� and� ground.� In� extended� mode� (Figure�

�4b),� the� watchdog� timeout� period� is� multiplied� by� 128.�

�For� example,� in� extended� mode,� a� 0.1μF� capacitor� gives�

�a� watchdog� timeout� period� of� 65s� (see� the� Extended-�

�Mode� Watchdog� Timeout� Period� vs.� C� SWT� graph� in� the�

�Typical� Operating� Characteristics).� To� disable� the� watch-�

�dog� timer� function,� connect� SWT� to� ground.�

�MAX6752/MAX6753�

�The� MAX6752� and� MAX6753� have� a� windowed� watch-�

�dog� timer� that� asserts� RESET� for� the� adjusted� reset�

�timeout� period� when� the� watchdog� recognizes� a� fast�

�watchdog� fault� (t� WDI� <� t� WD1� ),� or� a� slow� watchdog� fault�

�(period� >� t� WD2� ).� The� reset� timeout� period� is� adjusted�

�independently� of� the� watchdog� timeout� period.�

�The� slow� watchdog� period,� t� WD2� is� calculated� as� follows:�

�t� WD2� =� 0.65� x� 10� 9� x� C� SWT�

�with� t� WD2� in� seconds� and� C� SWT� in� Farads.�

�The� fast� watchdog� period,� t� WD1� ,� is� selectable� as� a� ratio�

�from� the� slow� watchdog� fault� period� (t� WD2� ).� Select� the�

�fast� watchdog� period� by� pinstrapping� SET0� and� SET1,�

�Maxim� Integrated�

�where� HIGH� is� V� CC� and� LOW� is� GND.� Table� 1� illus-�

�trates� the� SET0� and� SET1� configuration� for� the� 8,� 16,�

�and� 64� window� ratio� (� t� WD2� /t� WD1� ).�

�For� example,� if� C� SWT� is� 1500pF,� and� SET0� and� SET1� are�

�low,� then� t� WD2� is� 975ms� (typ)� and� t� WD1� is� 122ms� (typ).�

�RESET� asserts� if� the� watchdog� input� has� two� falling�

�edges� too� close� to� each� other� (faster� than� t� WD1� )� (Figure�

�5a)� or� falling� edges� that� are� too� far� apart� (slower� than�

�t� WD2� )� (Figure� 5b).� Normal� watchdog� operation� is� dis-�

�played� in� (Figure� 5c).� The� internal� watchdog� timer� is�

�cleared� when� a� WDI� falling� edge� is� detected� within� the�

�valid� watchdog� window� or� when� RESET� is� deasserted.�

�All� WDI� inputs� are� ignored� while� RESET� is� asserted.�

�The� watchdog� timer� begins� to� count� after� RESET� is�

�deasserted.� The� watchdog� timer� clears� and� begins� to�

�count� after� a� valid� WDI� falling� logic� input.� WDI� falling�

�transitions� within� periods� shorter� than� t� WD1� or� longer�

�than� t� WD2� force� RESET� to� assert� low� for� the� reset� time-�

�out� period.� WDI� falling� transitions� within� the� t� WD1� and�

�t� WD2� window� do� not� assert� RESET� .� WDI� transitions�

�between� t� WD1(min)� and� t� WD1(max)� or� t� WD2(min)� and�

�t� WD2(max)� are� not� guaranteed� to� assert� or� deassert� the�

�RESET� .� To� guarantee� that� the� window� watchdog� does�

�not� assert� the� RESET� ,� strobe� WDI� between� t� WD1(max)�

�and� t� WD2(min)� .� The� watchdog� timer� is� cleared� when�

�RESET� is� asserted� or� after� a� falling� transition� on� WDI� or�

�after� a� state� change� on� SET0� or� SET1.� Disable� the�

�watchdog� timer� by� connecting� SET0� high� and� SET1� low.�

�9�

�相关PDF资料 |

PDF描述 |

|---|---|

| M3FFK-2636J | IDC CABLE - MCF26K/MC26G/MCF26K |

| M3EEK-2636J | IDC CABLE - MCE26K/MC26G/MCE26K |

| M3CMK-3406R | IDC CABLE - MKC34K/MC34M/MCG34K |

| UKA1V220MDD1TD | CAP ALUM 22UF 35V 20% RADIAL |

| UPA1E681MPD1TD | CAP ALUM 680UF 25V 20% RADIAL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX6750KA30 | 制造商:Maxim Integrated Products 功能描述:SINGLE/DUAL-VOLT MICROPROC. RESET C - Rail/Tube |

| MAX6750KA30+ | 制造商:Maxim Integrated Products 功能描述:MAXIM MAX6750KA30+, SUPERVISORS - Tape and Reel 制造商:Maxim Integrated Products 功能描述:Maxim MAX6750KA30+, Microprocessor Supervisory Circuit 3V/Adj Reset Threshold 1.575V-5V 8-pin SOT23 |

| MAX6750KA30+T | 功能描述:监控电路 RoHS:否 制造商:STMicroelectronics 监测电压数: 监测电压: 欠电压阈值: 过电压阈值: 输出类型:Active Low, Open Drain 人工复位:Resettable 监视器:No Watchdog 电池备用开关:No Backup 上电复位延迟(典型值):10 s 电源电压-最大:5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:UDFN-6 封装:Reel |

| MAX6750KA30-T | 功能描述:监控电路 RoHS:否 制造商:STMicroelectronics 监测电压数: 监测电压: 欠电压阈值: 过电压阈值: 输出类型:Active Low, Open Drain 人工复位:Resettable 监视器:No Watchdog 电池备用开关:No Backup 上电复位延迟(典型值):10 s 电源电压-最大:5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:UDFN-6 封装:Reel |

| MAX6750KA31 | 制造商:Maxim Integrated Products 功能描述:SINGLE/DUAL-VOLT MICROPROC. RESET C - Rail/Tube |

发布紧急采购,3分钟左右您将得到回复。