- 您现在的位置:买卖IC网 > PDF目录18708 > MAX7032EVSYS-315 (Maxim Integrated)EVAL KIT MAX7032 PDF资料下载

参数资料

| 型号: | MAX7032EVSYS-315 |

| 厂商: | Maxim Integrated |

| 文件页数: | 18/32页 |

| 文件大小: | 0K |

| 描述: | EVAL KIT MAX7032 |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

�� �

�

�

�Low-Cost,� Crystal-Based,� Programmable,�

�ASK/FSK� Transceiver� with� Fractional-N� PLL�

�Crystal� Oscillator� (XTAL)�

�The� XTAL� oscillator� in� the� MAX7032� is� designed� to� pre-�

�sent� a� capacitance� of� approximately� 3pF� between� the�

�XTAL1� and� XTAL2� pins.� In� most� cases,� this� corre-�

�sponds� to� a� 4.5pF� load� capacitance� applied� to� the�

�external� crystal� when� typical� PCB� parasitics� are� added.�

�It� is� very� important� to� use� a� crystal� with� a� load�

�capacitance� that� is� equal� to� the� capacitance� of� the�

�MAX7032� crystal� oscillator� plus� PCB� parasitics.� If� a�

�crystal� designed� to� oscillate� with� a� different� load�

�capacitance� is� used,� the� crystal� is� pulled� away� from� its�

�stated� operating� frequency,� introducing� an� error� in� the�

�reference� frequency.� Crystals� designed� to� operate� with�

�higher� differential� load� capacitance� always� pull� the� ref-�

�erence� frequency� higher.�

�In� actuality,� the� oscillator� pulls� every� crystal.� The� crys-�

�tal’s� natural� frequency� is� really� below� its� specified� fre-�

�quency,� but� when� loaded� with� the� specified� load�

�capacitance,� the� crystal� is� pulled� and� oscillates� at� its�

�specified� frequency.� This� pulling� is� already� accounted�

�for� in� the� specification� of� the� load� capacitance.�

�Additional� pulling� can� be� calculated� if� the� electrical�

�parameters� of� the� crystal� are� known.� The� frequency�

�pulling� is� given� by:�

�where:�

�f� p� is� the� amount� the� crystal� frequency� is� pulled� in� ppm.�

�C� m� is� the� motional� capacitance� of� the� crystal.�

�C� CASE� is� the� case� capacitance.�

�C� SPEC� is� the� specified� load� capacitance.�

�C� LOAD� is� the� actual� load� capacitance.�

�When� the� crystal� is� loaded� as� specified,� i.e.,� C� LOAD� =�

�C� SPEC� ,� the� frequency� pulling� equals� zero.�

�Serial� Control� Interface�

�Communication� Protocol�

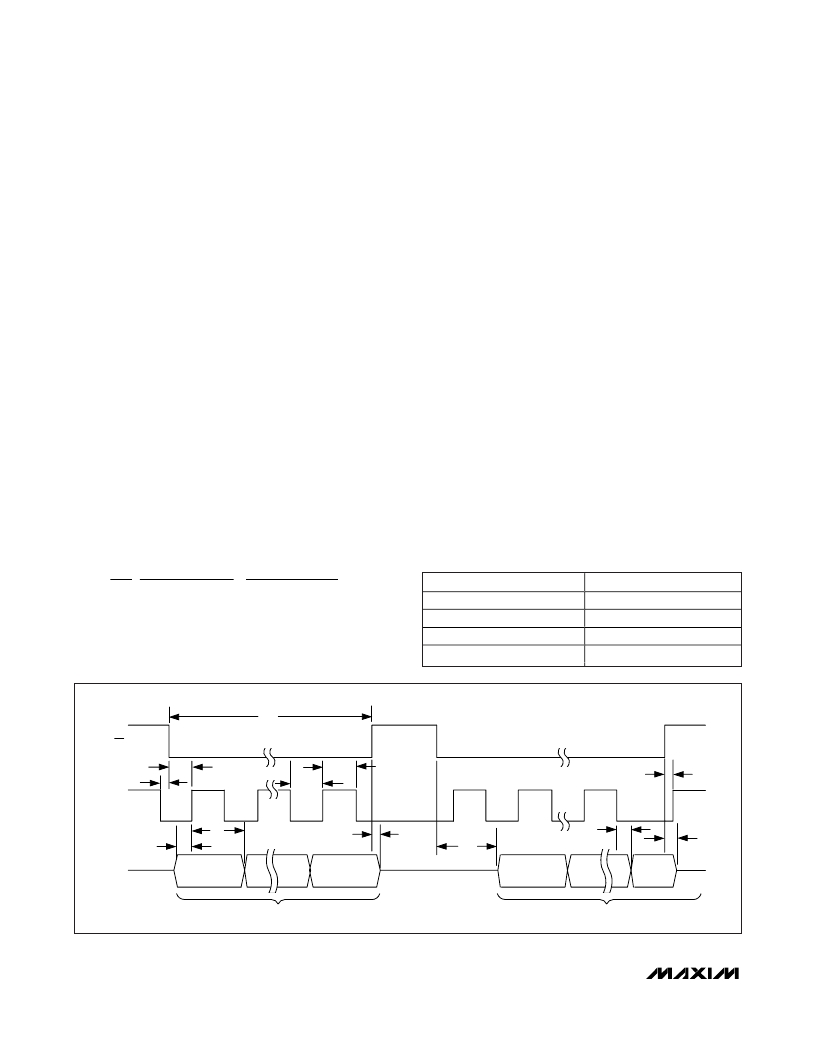

�The� MAX7032� programs� through� a� 3-wire� interface.� The�

�data� input� must� follow� the� timing� diagrams� shown� in�

�Figures� 7,� 8,� and� 9.�

�Note� that� the� DIO� line� must� be� held� LOW� while� CS� is�

�high.� This� is� to� prevent� the� MAX7032� from� entering� dis-�

�continuous� receive� mode� if� the� DRX� bit� is� high.� The�

�data� is� latched� on� the� rising� edge� of� SCLK,� and� there-�

�fore� must� be� stable� before� that� edge.� The� data�

�sequencing� is� MSB� first,� the� command� (C[1:0]� see�

�Table� 2),� the� register� address� (A[5:0]� see� Table� 3),� and�

�the� data� (D[7:0]� see� Table� 4).�

�C� m� ?� 1� 1� ?�

�?� C�

�C� CASE� +� C� SPEC� ?� ?�

�f� P� =�

�2� ?� CASE� +� C� LOAD�

�?�

�� 10� 6�

�Table� 2.� Command� Bits�

�C[1:0]�

�0x0�

�DESCRIPTION�

�No� operation�

�CS�

�t� CS�

�0x1�

�0x2�

�0x3�

�Write� data�

�Read� data�

�Master� reset�

�SCLK�

�t� SC�

�t� CSS�

�t� CL�

�t� CH�

�t� CSH�

�t� DS�

�t� DH�

�t� TH�

�t� DV�

�t� DO�

�t� TR�

�DIO�

�HI-Z�

�HI-Z�

�D7�

�D0�

�HI-Z�

�DATA� IN�

�Figure� 7.� Serial� Interface� Timing� Diagram�

�DATA� OUT�

�18�

�______________________________________________________________________________________�

�相关PDF资料 |

PDF描述 |

|---|---|

| 1583514-1 | TOOLING UPPER MTA 050 |

| GLAA07B | SWITCH TOP PLUNGER SNAP SPDT |

| GLAA01C | SWITCH TOP ROLLR PLNGR SNAP SPDT |

| GLAC01C | SWTCH TOP ROLLR PLUNGR SNAP SPDT |

| DM1810-434-DK | DM1810 433.92 MHZ DEVELOPMENT KI |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX7032EVSYS-433 | 功能描述:射频开发工具 MAX7032 Eval Kit RoHS:否 制造商:Taiyo Yuden 产品:Wireless Modules 类型:Wireless Audio 工具用于评估:WYSAAVDX7 频率: 工作电源电压:3.4 V to 5.5 V |

| MAX7033 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:315MHz/433MHz ASK Superheterodyne Receiver with AGC Lock |

| MAX7033_1 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Evaluation Kit |

| MAX7033_11 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:315MHz/433MHz ASK Superheterodyne Receiver with AGC Lock |

| MAX7033_1109 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:315MHz/433MHz ASK Superheterodyne Receiver with AGC Lock |

发布紧急采购,3分钟左右您将得到回复。