- 您现在的位置:买卖IC网 > PDF目录11683 > MAX9244GUM+D (Maxim Integrated Products)IC 21BIT DESERIALIZER 48-TSSOP PDF资料下载

参数资料

| 型号: | MAX9244GUM+D |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 11/23页 |

| 文件大小: | 0K |

| 描述: | IC 21BIT DESERIALIZER 48-TSSOP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 39 |

| 功能: | 解串器 |

| 数据速率: | 306Mbps |

| 输入类型: | LVDS |

| 输出类型: | LVTTL,LVCMOS |

| 输入数: | 3 |

| 输出数: | 21 |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-TFSOP(0.240",6.10mm 宽) |

| 供应商设备封装: | 48-TSSOP |

| 包装: | 管件 |

MAX9242/MAX9244/MAX9246/MAX9254

21-Bit Deserializers with Programmable

Spread Spectrum and DC Balance

______________________________________________________________________________________

19

Link Power-Up Sequence

The recommended link power-up sequence is to power

up the serializer, wait until the serializer PLL locks, and

then power up the deserializer. This sequence prevents

the deserializer from seeing an undriven or unstable

input when powering up.

PWRDWN

Driving PWRDWN low puts the outputs in high imped-

ance, stops the PLL, and reduces supply current to

50A or less. Driving PWRDWN high drives the outputs

low until the PLL locks. The outputs of two deserializers

can be bused to form a 2:1 mux with the outputs con-

trolled by PWRDWN. Wait 100ns between disabling one

deserializer (driving PWRDWN low) and enabling the

second one (driving PWRDWN high) to avoid con-

tention of the bused outputs.

Power-Supply Bypassing

There are separate on-chip power domains for digital

circuits, outputs, PLL, and LVDS inputs. Bypass each

VCC, VCCO, PLLVCC, and LVDSVCC with high-frequency,

surface-mount ceramic 0.1F and 0.001F capacitors in

parallel as close to the device as possible, with the

smallest value capacitor closest to the supply pin.

Cables and Connectors

Interconnect for LVDS typically has a differential imped-

ance of 100

Ω. Use cables and connectors that have

matched differential impedance to minimize impedance

discontinuities.

Twisted-pair and shielded twisted-pair cables offer

superior signal quality compared to ribbon cable and

tend to generate less EMI due to magnetic field cancel-

ing effects. Balanced cables pick up noise as common

mode, which is rejected by the LVDS receiver.

Board Layout

Keep the LVTTL/LVCMOS outputs and LVDS input sig-

nals separated to prevent crosstalk. A four-layer PC

board with separate layers for power, ground, LVDS

inputs, and digital signals is recommended. Layout PC

board traces for 100

Ω differential characteristic imped-

ance. The trace dimensions depend on the type of

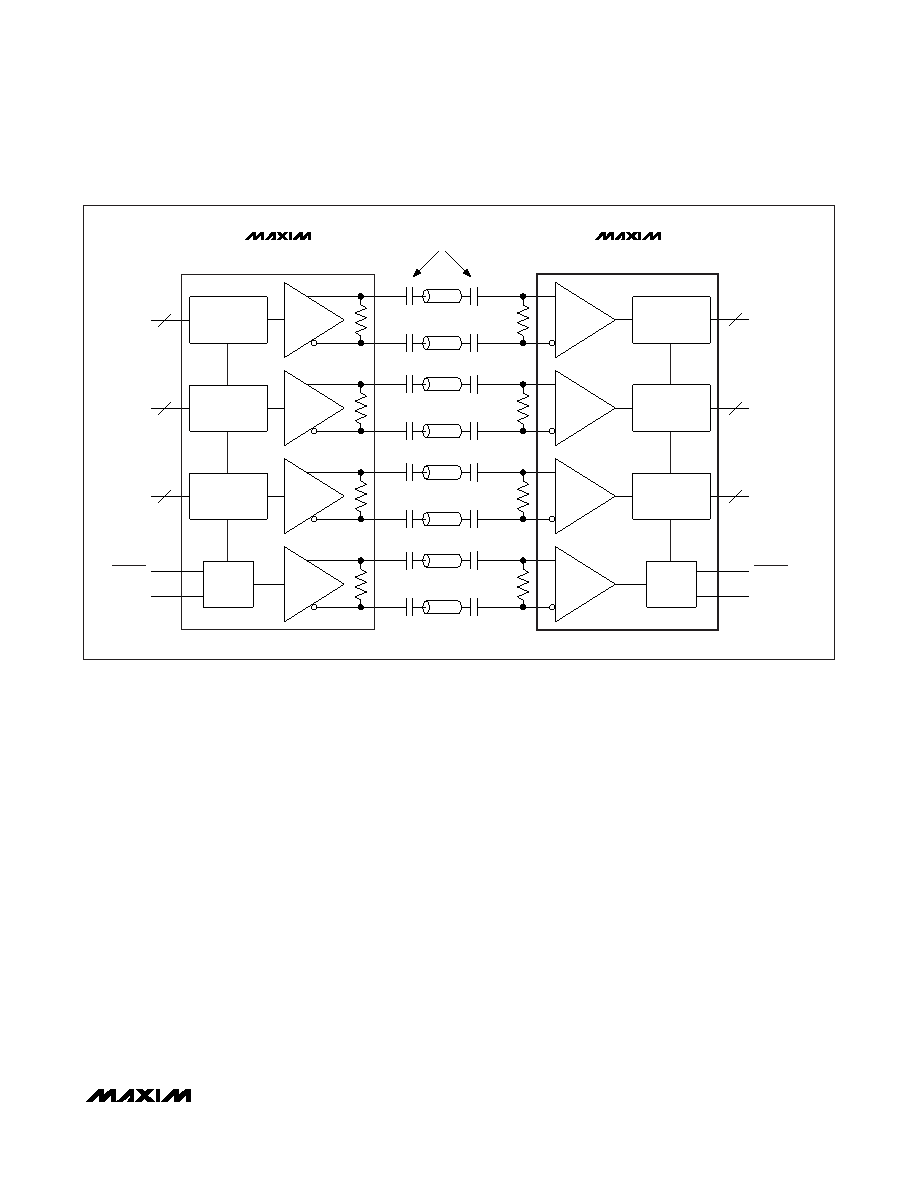

(7 + 2):1

7

100

Ω

(7 + 2):1

7

100

Ω

(7 + 2):1

7

100

Ω

PLL

100

Ω

MAX9209/MAX9213

MAX9242/MAX9244/MAX9246/MAX9254

TxOUT

TxCLK OUT

RxIN__

RxCLK IN

21:3 SERIALIZER

3:21 DESERIALIZER

PWRDWN

RxCLK OUT

RxOUT_

PWRDWN

TxCLK IN

TxIN

HIGH-FREQUENCY CERAMIC

SURFACE-MOUNT CAPACITORS

PLL1 +

SSPLL

1:(9 - 2)

+ FIFO

1:(9 - 2)

+ FIFO

1:(9 - 2)

+ FIFO

RO

RT

Figure 20. Four Capacitors per Link, AC-Coupled, DC-Balanced Mode

相关PDF资料 |

PDF描述 |

|---|---|

| MAX9242GUM+D | IC 21BIT DESERIALIZER 48-TSSOP |

| VI-B6W-IW-F3 | CONVERTER MOD DC/DC 5.5V 100W |

| 031-2301 | CONN TNC RCPT BULKHEAD FRONT MNT |

| MAX9254EUM/V+ | IC DESERIALIZER 21BIT 48TSSOP |

| VI-B6W-IW-F2 | CONVERTER MOD DC/DC 5.5V 100W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX9246 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:21-Bit Deserializers with Programmable Spread Spectrum and DC Balance |

| MAX9246EUM | 功能描述:LVDS 接口集成电路 RoHS:否 制造商:Texas Instruments 激励器数量:4 接收机数量:4 数据速率:155.5 Mbps 工作电源电压:5 V 最大功率耗散:1025 mW 最大工作温度:+ 85 C 封装 / 箱体:SOIC-16 Narrow 封装:Reel |

| MAX9246EUM/V+ | 功能描述:串行器/解串器 - Serdes 21-Bit DC-Balanced LVDS Deserializer RoHS:否 制造商:Texas Instruments 类型:Deserializer 数据速率:1.485 Gbit/s 输入类型:ECL/LVDS 输出类型:LVCMOS 输入端数量:1 输出端数量:20 工作电源电压:2.375 V to 2.625 V 工作温度范围:0 C to + 70 C 封装 / 箱体:TQFP-64 |

| MAX9246EUM/V+T | 功能描述:串行器/解串器 - Serdes 21-Bit DC-Balanced LVDS Deserializer RoHS:否 制造商:Texas Instruments 类型:Deserializer 数据速率:1.485 Gbit/s 输入类型:ECL/LVDS 输出类型:LVCMOS 输入端数量:1 输出端数量:20 工作电源电压:2.375 V to 2.625 V 工作温度范围:0 C to + 70 C 封装 / 箱体:TQFP-64 |

| MAX9246EUM+D | 功能描述:串行器/解串器 - Serdes 21-Bit DC-Balanced LVDS Deserializer RoHS:否 制造商:Texas Instruments 类型:Deserializer 数据速率:1.485 Gbit/s 输入类型:ECL/LVDS 输出类型:LVCMOS 输入端数量:1 输出端数量:20 工作电源电压:2.375 V to 2.625 V 工作温度范围:0 C to + 70 C 封装 / 箱体:TQFP-64 |

发布紧急采购,3分钟左右您将得到回复。