- 您现在的位置:买卖IC网 > PDF目录11683 > MAX9244GUM+D (Maxim Integrated Products)IC 21BIT DESERIALIZER 48-TSSOP PDF资料下载

参数资料

| 型号: | MAX9244GUM+D |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 8/23页 |

| 文件大小: | 0K |

| 描述: | IC 21BIT DESERIALIZER 48-TSSOP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 39 |

| 功能: | 解串器 |

| 数据速率: | 306Mbps |

| 输入类型: | LVDS |

| 输出类型: | LVTTL,LVCMOS |

| 输入数: | 3 |

| 输出数: | 21 |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-TFSOP(0.240",6.10mm 宽) |

| 供应商设备封装: | 48-TSSOP |

| 包装: | 管件 |

MAX9242/MAX9244/MAX9246/MAX9254

21-Bit Deserializers with Programmable

Spread Spectrum and DC Balance

16

______________________________________________________________________________________

DC-coupled link (2.4V - 1.425V = 0.975V and 1.075V -

0V = 1.075V). Common-mode voltage differences may

be due to ground potential variation or common-mode

noise. If there is more than

±1V of difference, the receiver

is not guaranteed to read the input signal correctly and

may cause bit errors. AC-coupling filters low-frequency

ground shifts and common-mode noise and passes

high-frequency data. A common-mode voltage differ-

ence up to the voltage rating of the coupling capacitor

(minus half the differential swing) is tolerated. DC-bal-

anced coding of the data is required to maintain the

differential signal amplitude and limit jitter on an

AC-coupled link. A capacitor in series with each output

of the LVDS driver is sufficient for AC-coupling. However,

two capacitors—one at the serializer output and one at

the deserializer input—provide protection in case either

end of the cable is shorted to a high voltage.

Applications Information

Selection of AC-Coupling Capacitors

Voltage droop and the DSV of transmitted symbols

cause signal transitions to start from different voltage

levels. Because the transition time is finite, starting the

signal transition from different voltage levels causes

timing jitter. The time constant for an AC-coupled link

needs to be chosen to reduce droop and jitter to an

acceptable level.

The RC network for an AC-coupled link consists of the

LVDS receiver termination resistor (RT), the LVDS driver

output resistor (RO), and the series AC-coupling capac-

itors (C). The RC time constant for two equal-value

series capacitors is (C x (RT + RO)) / 2 (Figure 19). The

RC time constant for four equal-value series capacitors

is (C x (RT + RO)) / 4 (Figure 20).

RPLLS (65,600 x RCIP)

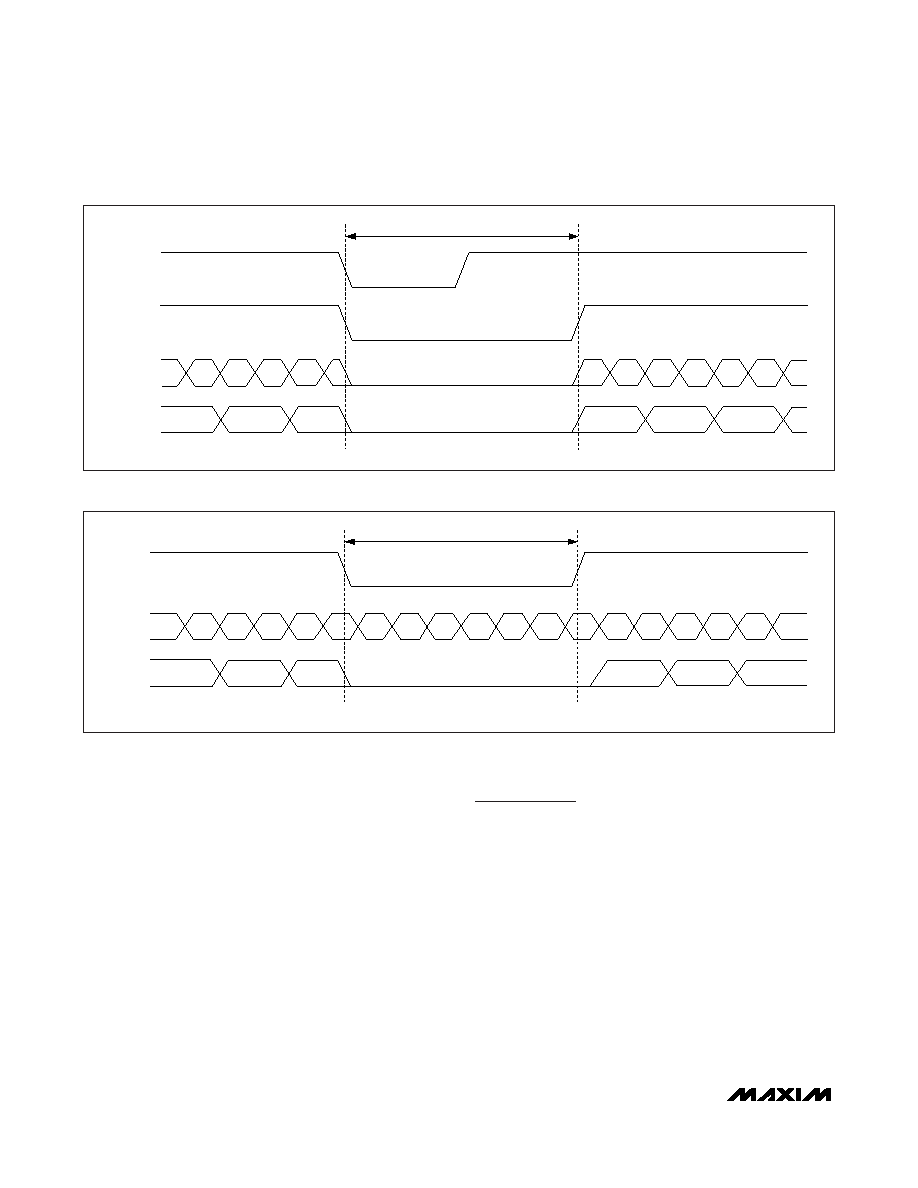

LOW

RxCLKOUT

INTERNAL

PLL1 LOCK

INTERNAL

SSPLL LOCK

RxOUT_

LOW

Figure 16. Output Waveforms when PLL1 Loses Lock and Locks Again

RPLLS2 (32,800 x RCIP)

LOW

INTERNAL

SSPLL LOCK

RxCLKOUT

RxOUT_

TIMING SHOWN FOR STABLE CLOCK AND DATA INPUTS

Figure 17. Output Waveforms if Spread-Spectrum PLL Loses Lock and Locks Again

相关PDF资料 |

PDF描述 |

|---|---|

| MAX9242GUM+D | IC 21BIT DESERIALIZER 48-TSSOP |

| VI-B6W-IW-F3 | CONVERTER MOD DC/DC 5.5V 100W |

| 031-2301 | CONN TNC RCPT BULKHEAD FRONT MNT |

| MAX9254EUM/V+ | IC DESERIALIZER 21BIT 48TSSOP |

| VI-B6W-IW-F2 | CONVERTER MOD DC/DC 5.5V 100W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX9246 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:21-Bit Deserializers with Programmable Spread Spectrum and DC Balance |

| MAX9246EUM | 功能描述:LVDS 接口集成电路 RoHS:否 制造商:Texas Instruments 激励器数量:4 接收机数量:4 数据速率:155.5 Mbps 工作电源电压:5 V 最大功率耗散:1025 mW 最大工作温度:+ 85 C 封装 / 箱体:SOIC-16 Narrow 封装:Reel |

| MAX9246EUM/V+ | 功能描述:串行器/解串器 - Serdes 21-Bit DC-Balanced LVDS Deserializer RoHS:否 制造商:Texas Instruments 类型:Deserializer 数据速率:1.485 Gbit/s 输入类型:ECL/LVDS 输出类型:LVCMOS 输入端数量:1 输出端数量:20 工作电源电压:2.375 V to 2.625 V 工作温度范围:0 C to + 70 C 封装 / 箱体:TQFP-64 |

| MAX9246EUM/V+T | 功能描述:串行器/解串器 - Serdes 21-Bit DC-Balanced LVDS Deserializer RoHS:否 制造商:Texas Instruments 类型:Deserializer 数据速率:1.485 Gbit/s 输入类型:ECL/LVDS 输出类型:LVCMOS 输入端数量:1 输出端数量:20 工作电源电压:2.375 V to 2.625 V 工作温度范围:0 C to + 70 C 封装 / 箱体:TQFP-64 |

| MAX9246EUM+D | 功能描述:串行器/解串器 - Serdes 21-Bit DC-Balanced LVDS Deserializer RoHS:否 制造商:Texas Instruments 类型:Deserializer 数据速率:1.485 Gbit/s 输入类型:ECL/LVDS 输出类型:LVCMOS 输入端数量:1 输出端数量:20 工作电源电压:2.375 V to 2.625 V 工作温度范围:0 C to + 70 C 封装 / 箱体:TQFP-64 |

发布紧急采购,3分钟左右您将得到回复。