- 您现在的位置:买卖IC网 > PDF目录8921 > MAX9485ETP+T (Maxim Integrated Products)IC CLOCK GENERATOR AUD 20-TQFN PDF资料下载

参数资料

| 型号: | MAX9485ETP+T |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 2/16页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GENERATOR AUD 20-TQFN |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 2,500 |

| 类型: | 时钟发生器 |

| PLL: | 是 |

| 输入: | LVCMOS,LVTTL,晶体 |

| 输出: | LVCMOS,LVTTL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:3 |

| 差分 - 输入:输出: | 无/无 |

| 频率 - 最大: | 73.728MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-WFQFN 裸露焊盘 |

| 供应商设备封装: | 20-TQFN-EP(4x4) |

| 包装: | 带卷 (TR) |

MAX9485

Software Mode Programming

(MODE = Low)

In software mode, the I2C interface writes or reads an

8-bit control register in the MAX9485. The control regis-

ter controls the rate settings and the clock outputs.

Since there is only one register in the MAX9485, no

address is assigned to this register. The device has a

programmable 7-bit address for the I2C bus, selected

by SAO1 and SAO2 (Table 8). At power-up with MODE

= low, the MAX9485 reads the state of SAO1 and

SAO2, then latches the I2C device address. Table 9

shows the control register bit mapping. Bit C7 enables

the MCLK output. Bits C5 and C6 enable the clock out-

puts CLK_OUT1 and CLK_OUT2, respectively. Bit C4

selects the sampling rates. Bits C3 and C2 choose the

output frequency-scaling factor. Bits C1 and C0 deter-

mine the sampling frequency. The details are shown in

Tables 10–14.

Serial Interface

The MAX9485 control interface uses a 2-wire I2C serial

interface. The device operates as a slave that sends

and receives data through clock line SCL and data line

SDA to achieve bidirectional communication with the

master. A master (typically a microcontroller) initiates all

data transfers to and from the MAX9485, and generates

the SCL clock that synchronizes the data transfer. The

Programmable Audio Clock Generator

10

______________________________________________________________________________________

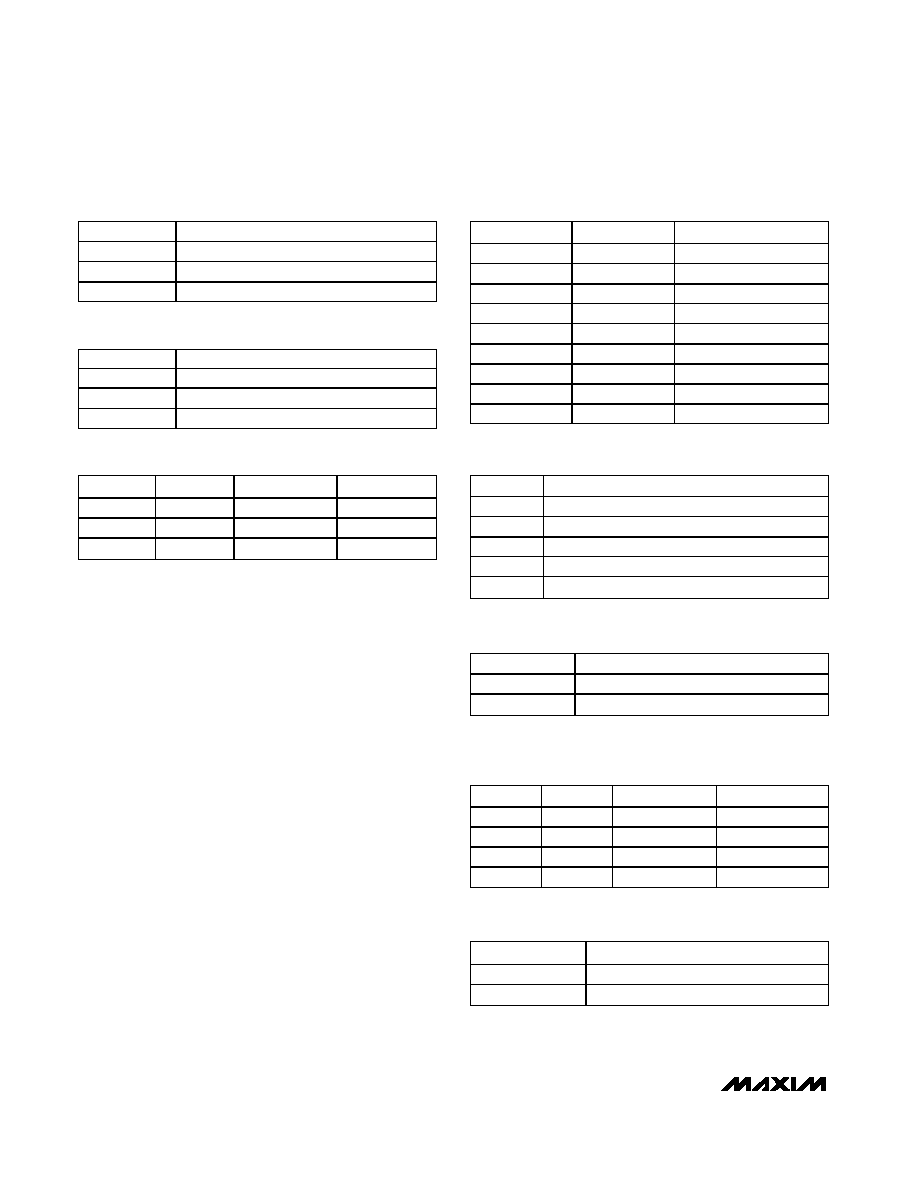

FS0

SAMPLING FREQUENCY (kHz)

Low

32

High

44.1

Open

48

Table 5. Selection of Sampling Frequency

SAO1

SAO2

I

2C DEVICE ADDRESS

Open

110 0000

Low

Open

110 0011

High

Open

110 0010

Open

Low

110 0100

Low

110 1000

High

Low

111 0000

Open

High

111 0001

Low

High

111 0010

High

111 0100

Table 8. Register Address Selection

BIT

FUNCTION

C7

MCLK enable/disable

C6, C5

CLK_OUT2, CLK_OUT1 enable/disable

C4

Sampling-rate selection

C3, C2

Frequency-scaling factors

C1, C0

Sampling-frequency selection

Table 9. Control Register Bit Mapping

C7

MCLK

0

Disabled

1

Enabled

Table 10. MCLK Enable/Disable Control

C6

C5

CLK_OUT2

CLK_OUT1

1

Enabled

1

0

Enabled

Disabled

0

1

Disabled

Enabled

0

Disabled

Table 11. CLK_OUT1, 2 Enable/Disable

Control

C4

SAMPLING RATE

0

Standard

1

Doubled

Table 12. Sampling Rate Selection

SAO1

MCLK

Low

Disabled

High

Enabled

Open

Reserved

Table 6. MCLK Enable/Disable Control

SAO1

SAO2

CLK_OUT1

CLK_OUT2

High/low

Open

Enabled

High/low

Low

Enabled

Disabled

High/low

High

Disabled

Enabled

Table 7. CLK_OUT Enable/Disable Control

相关PDF资料 |

PDF描述 |

|---|---|

| MS3120P16-26S | CONN RCPT 26POS WALL MNT W/SCKT |

| MCP4901-E/P | DAC 8BIT SGL W/SPI 8PDIP |

| MCP4901-E/MS | DAC 8BIT SGL W/SPI 8MSOP |

| VE-B1M-MV-F1 | CONVERTER MOD DC/DC 10V 150W |

| MAX9485EUP+T | IC CLOCK GEN PROG 20TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX9485EUP | 功能描述:时钟发生器及支持产品 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MAX9485EUP+ | 功能描述:时钟发生器及支持产品 Programmable Audio Clock Generator RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MAX9485EUP+T | 功能描述:时钟发生器及支持产品 Programmable Audio Clock Generator RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MAX9485EUP-T | 功能描述:时钟发生器及支持产品 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MAX9485EVKIT | 制造商:Maxim Integrated Products 功能描述:PROGRAMMABLE AUDIO CLOCK GENERATOR - Bulk |

发布紧急采购,3分钟左右您将得到回复。