- 您现在的位置:买卖IC网 > PDF目录10965 > MAX9526AEI/V+ (Maxim Integrated Products)IC VID DECODER NTSC/PAL 28QSOP PDF资料下载

参数资料

| 型号: | MAX9526AEI/V+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 25/38页 |

| 文件大小: | 0K |

| 描述: | IC VID DECODER NTSC/PAL 28QSOP |

| 其它有关文件: | Automotive Product Guide |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 50 |

| 类型: | 视频解码器 |

| 应用: | 车载系统,播放器,电视 |

| 电压 - 电源,模拟: | 1.8V |

| 电压 - 电源,数字: | 1.8V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-SSOP(0.154",3.90mm 宽) |

| 供应商设备封装: | 28-QSOP |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页

Low-Power, High-Performance

NTSC/PAL Video Decoder

ITU-R BT.656 Standard Clipping Level (CLIP)

1 = Clip ITU output to Y range is between 64–940 and

CbCr range is between 64–960.

0 = Clip ITU output to Y range and CbCr range is

between 5–1019 (default).

Inverted Line-Locked Clock (LLC_INV)

This signal inverts the polarity of the line-locked clock

that is output from the MAX9526. This can be used to

solve board level timing problems for other devices.

1 = Invert LLC clock.

0 = Do not invert LLC clock (default).

Input Clock Frequency Select (SEL_54MHz)

1 = 54MHz clock at XTAL/OSC input.

0 = 27MHz clock at XTAL/OSC input (default).

This bit is only applicable when the crystal oscillator is

disabled (XTAL_DIS = 1).

Crystal Oscillator Disable (XTAL_DIS)

1 = XTAL/OSC is either a 27MHz or a 54MHz CMOS

clock input.

0 = Enables the 27MHz crystal oscillator (default).

Horizontal/Vertical Sync Output (HSVS)

1 = D1 and D0 output horizontal and vertical sync

pulses, respectively.

0 = D1 and D0 are LSBs of digital component video

output (default).

The rising edge of horizontal sync (HS) coincides with

the end of active video (rises after 3FFh 000h of EAV

code). The falling edge coincides with the start of

active video (SAV) code (falls after completing 3FFh

000h of SAV code). Figure 18 shows the horizontal and

vertical sync timing.

The vertical sync pulse (VS) line transitions are detailed

in Table 8. Note that the VS line transitions on pin D0

are shifted by 1 to 2 lines relative to the V flag transi-

tions embedded in the ITU data stream. The V flag tran-

sitions embedded in the ITU data stream follow the

ITU-R BT.656-4 standard.

Data Output Disable (DATAZ)

1 = Logic data outputs (D9–D0) are disabled and

placed in high-impedance state.

0 = Logic data outputs (D9–D0) are enabled (default).

The DATAZ bit forces data outputs high impedance

regardless of whether the device is in shutdown.

Clock Output Disable (LLCZ)

1 = Logic clock output (LLC) is disabled and placed

in a high-impedance state.

0 = Logic clock output (LLC) is enabled (default).

The LLCZ bit forces LLC high impedance regardless of

whether the device is in shutdown.

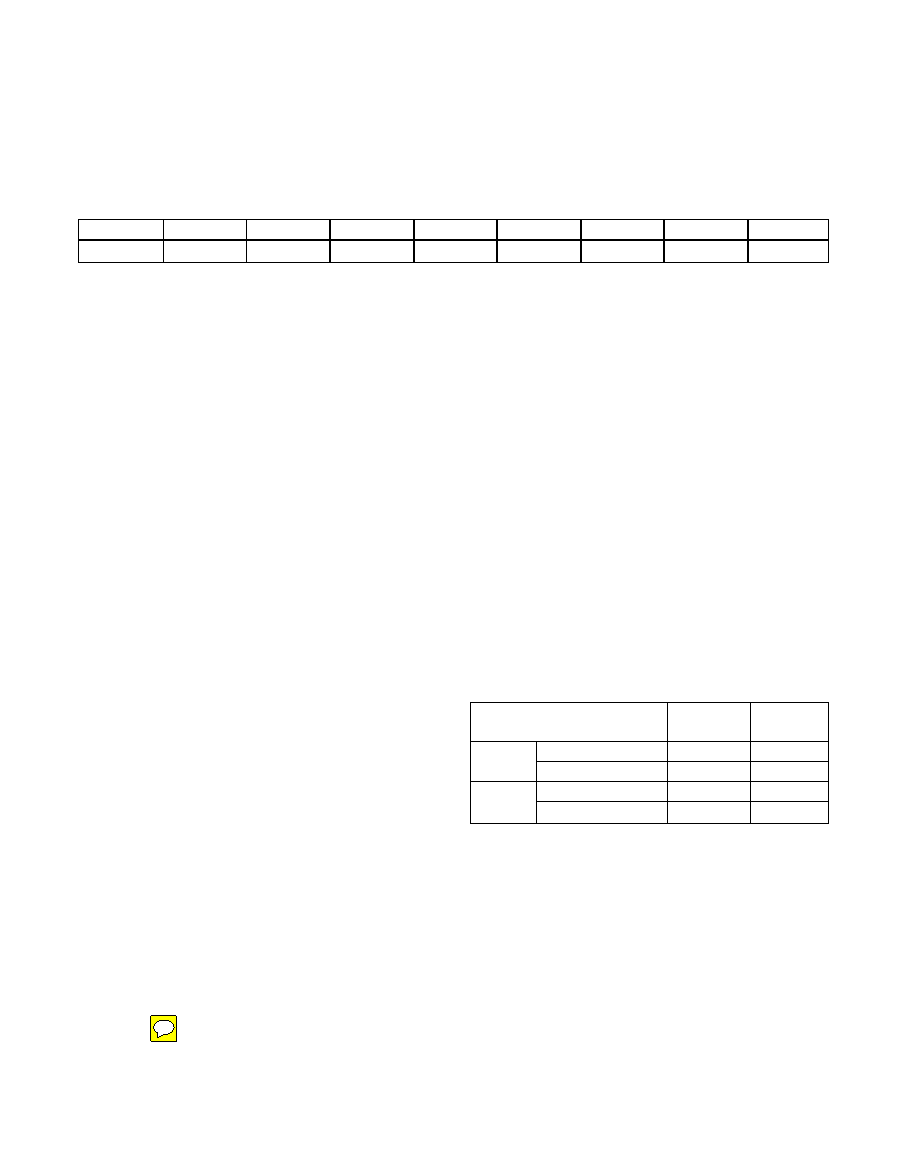

REG

B7

B6

B5

B4

B3

B2

B1

B0

0x0D

0

CLIP

LLC_INV

SEL_54MHZ

XTAL_DIS

HSVS

DATAZ

LLCZ

Clock and Output Control Register

VERTICAL SYNC PULSES

(VS on Pin D0)

625

525

Start (VS = 1)

Line 623

Line 2

Field 1

Finish (VS = 0)

Line 21

Start (VS = 1)

Line 309

Line 265

Field 2

Finish (VS = 0)

Line 335

Line 284

Table 8. VS (Pin D0) Line Transitions

MAX9526

Maxim Integrated

31

相关PDF资料 |

PDF描述 |

|---|---|

| VE-2NK-IY-F1 | CONVERTER MOD DC/DC 40V 50W |

| VE-B4T-IX-B1 | CONVERTER MOD DC/DC 6.5V 75W |

| VE-2NJ-IY-F3 | CONVERTER MOD DC/DC 36V 50W |

| VI-BWH-IY-F4 | CONVERTER MOD DC/DC 52V 50W |

| VE-B4L-IX-B1 | CONVERTER MOD DC/DC 28V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX9526ATJ/V+ | 功能描述:视频 IC Low-Power High-Performance NTSC/PAL Video Decoder RoHS:否 制造商:Fairchild Semiconductor 工作电源电压:5 V 电源电流:80 mA 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-28 封装:Reel |

| MAX9526ATJ/V+T | 功能描述:视频 IC Low-Power High-Performance NTSC/PAL Video Decoder RoHS:否 制造商:Fairchild Semiconductor 工作电源电压:5 V 电源电流:80 mA 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-28 封装:Reel |

| MAX9526ATJ+ | 功能描述:视频 IC NTSC/PAL Video Decoder RoHS:否 制造商:Fairchild Semiconductor 工作电源电压:5 V 电源电流:80 mA 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-28 封装:Reel |

| MAX9526ATJ+T | 功能描述:视频 IC NTSC/PAL Video Decoder RoHS:否 制造商:Fairchild Semiconductor 工作电源电压:5 V 电源电流:80 mA 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-28 封装:Reel |

| MAX9526EVKIT+ | 功能描述:视频 IC 开发工具 MAX9526 Eval Kit RoHS:否 制造商:Texas Instruments 产品:Evaluation Boards 类型:YPbPr to RGBHV Converters 工具用于评估:LMH1251 工作电源电压:5 V |

发布紧急采购,3分钟左右您将得到回复。