- 您现在的位置:买卖IC网 > PDF目录80427 > MB95F106ANWPFV 8-BIT, FLASH, 16.25 MHz, MICROCONTROLLER, PQFP64 PDF资料下载

参数资料

| 型号: | MB95F106ANWPFV |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, FLASH, 16.25 MHz, MICROCONTROLLER, PQFP64 |

| 封装: | 10 X 10 MM, 1.70 MM HEIGHT, 0.50 MM PITCH, PLASTIC, LQFP-64 |

| 文件页数: | 53/72页 |

| 文件大小: | 1851K |

| 代理商: | MB95F106ANWPFV |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页当前第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页

MB95100AM Series

DS07-12614-3E

57

(Vcc

= 5.0 V ± 10%, AVss = Vss = 0.0 V, TA = 40 °C to + 85 °C)

(Continued)

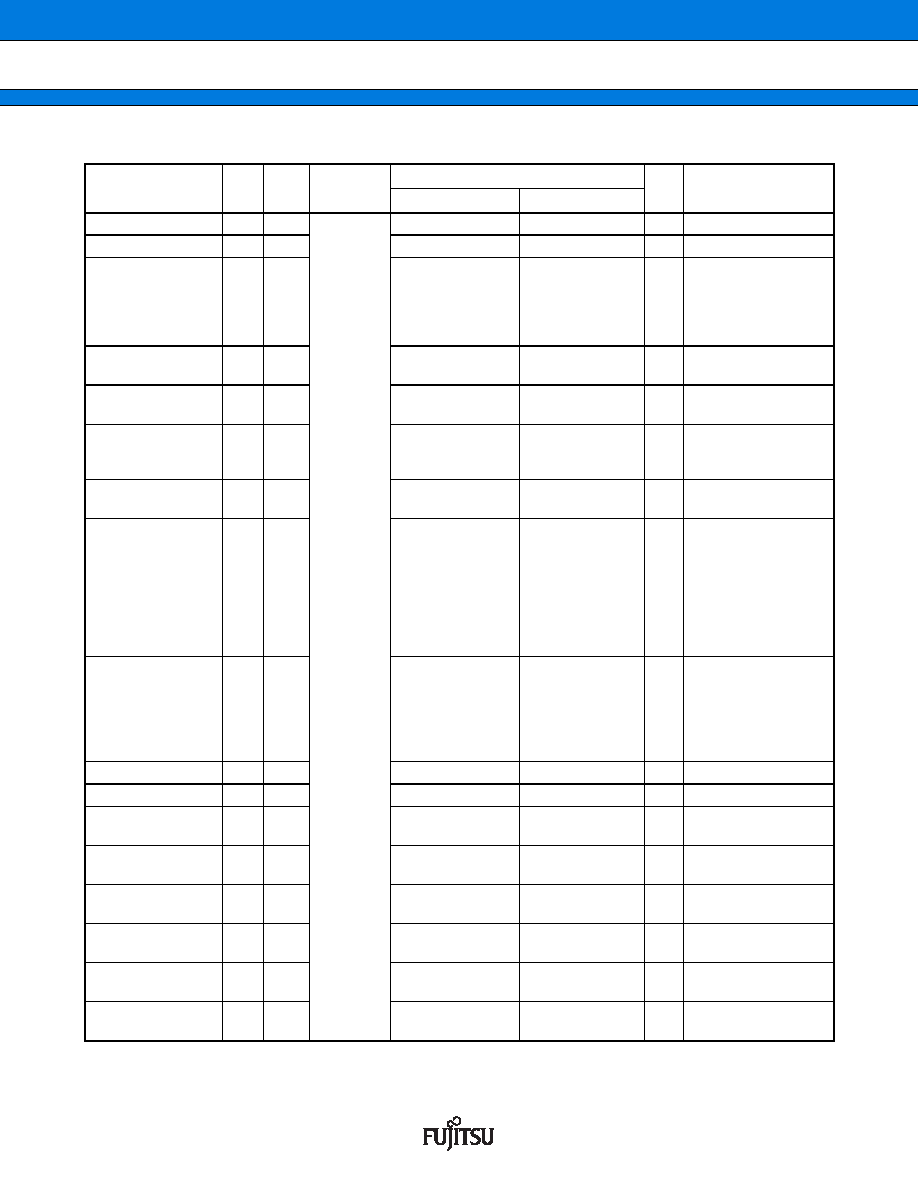

Parameter

Sym-

bol

Pin

name

Condition

Value*2

Unit

Remarks

Min

Max

SCL clock “L” width

tLOW

SCL0

R

= 1.7 k,

C

= 50 pF*1

(2

+ nm / 2) tMCLK 20

ns

Master mode

SCL clock “H” width

tHIGH

SCL0

(nm

/ 2) tMCLK 20

(nm

/ 2 ) tMCLK + 20

ns

Master mode

Start condition hold

time

tHD;STA

SCL0

SDA0

(

1 + nm / 2) tMCLK 20 (1 + nm) tMCLK + 20

ns

Master mode

Maximum value is

applied when m, n

= 1, 8.

Otherwise, the minimum

value is applied.

Stop condition setup

time

tSU;STO

SCL0

SDA0

(1

+ nm / 2) tMCLK 20 (1 + nm / 2) tMCLK + 20

ns

Master mode

Start condition setup

time

tSU;STA

SCL0

SDA0

(1

+ nm / 2) tMCLK 20 (1 + nm / 2) tMCLK + 20

ns

Master mode

Bus free time between

stop condition and

start condition

tBUF

SCL0

SDA0

(2 nm

+ 4) tMCLK 20

ns

Data hold time

tHD;DAT

SCL0

SDA0

3 tMCLK

20

ns

Master mode

Data setup time

tSU;DAT

SCL0

SDA0

(

2 + nm / 2) tMCLK 20 (1 + nm / 2) tMCLK + 20 ns

Master mode

When assuming that “L”

of SCL is not extended,

the minimum value is

applied to first bit of

continuous data.

Otherwise, the maximum

value is applied.

Setup time between

clearing interrupt and

SCL rising

tSU;INT SCL0

(nm

/ 2) tMCLK 20

(1 + nm

/ 2) tMCLK + 20

ns

Minimum value is

applied to interrupt at 9th

SCL

↓.

Maximum value is

applied to interrupt at 8th

SCL

↓.

SCL clock “L” width

tLOW

SCL0

4 tMCLK

20

ns

At reception

SCL clock “H” width

tHIGH

SCL0

4 tMCLK

20

ns

At reception

Start condition

detection

tHD;STA

SCL0

SDA0

2 tMCLK

20

ns

Undetected when 1 tMCLK

is used at reception

Stop condition

detection

tSU;STO

SCL0

SDA0

2 tMCLK

20

ns

Undetected when 1 tMCLK

is used at reception

Restart detection

condition

tSU;STA

SCL0

SDA0

2 tMCLK

20

ns

Undetected when 1 tMCLK

is used at reception

Bus free time

tBUF

SCL0

SDA0

2 tMCLK

20

ns

At reception

Data hold time

tHD;DAT

SCL0

SDA0

2 tMCLK

20

ns

At slave transmission

mode

Data setup time

tSU;DAT

SCL0

SDA0

tLOW

3 tMCLK 20

ns

At slave transmission

mode

相关PDF资料 |

PDF描述 |

|---|---|

| MC68HC705P6ACDWER2 | 8-BIT, OTPROM, 2.1 MHz, MICROCONTROLLER, PDSO28 |

| M38022M2-XXXFP | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP64 |

| MB90346ESPMC | 16-BIT, MROM, 24 MHz, MICROCONTROLLER, PQFP100 |

| M38037M6-XXXHP | 8-BIT, MROM, 8.4 MHz, MICROCONTROLLER, PQFP64 |

| M37540M4-XXXSP | 8-BIT, MROM, 6 MHz, MICROCONTROLLER, PDIP32 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MB95F106JSPFM-GE1 | 制造商:FUJITSU 功能描述:8BIT MCU 32K FLASH 1K RAM QFP64 |

| MB95F108AHWPMC1-GSE2 | 制造商:FUJITSU 功能描述: |

| MB95F108AHWPMC1-G-SPE1 | 制造商:FUJITSU 功能描述: |

| MB95F108AHWPMC1-GS-SPE2 | 制造商:FUJITSU 功能描述: |

| MB95F108AJS | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:8-bit Proprietary Microcontrollers |

发布紧急采购,3分钟左右您将得到回复。