- 您现在的位置:买卖IC网 > PDF目录80431 > MB9AF311LPMC 32-BIT, FLASH, 40 MHz, RISC MICROCONTROLLER, PQFP64 PDF资料下载

参数资料

| 型号: | MB9AF311LPMC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, FLASH, 40 MHz, RISC MICROCONTROLLER, PQFP64 |

| 封装: | 0.65 MM PITCH, PLASTIC, LQFP-64 |

| 文件页数: | 107/114页 |

| 文件大小: | 1357K |

| 代理商: | MB9AF311LPMC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页当前第107页第108页第109页第110页第111页第112页第113页第114页

ATmega48PA/88PA/168PA [DATASHEET]

9223F–AVR–04/14

92

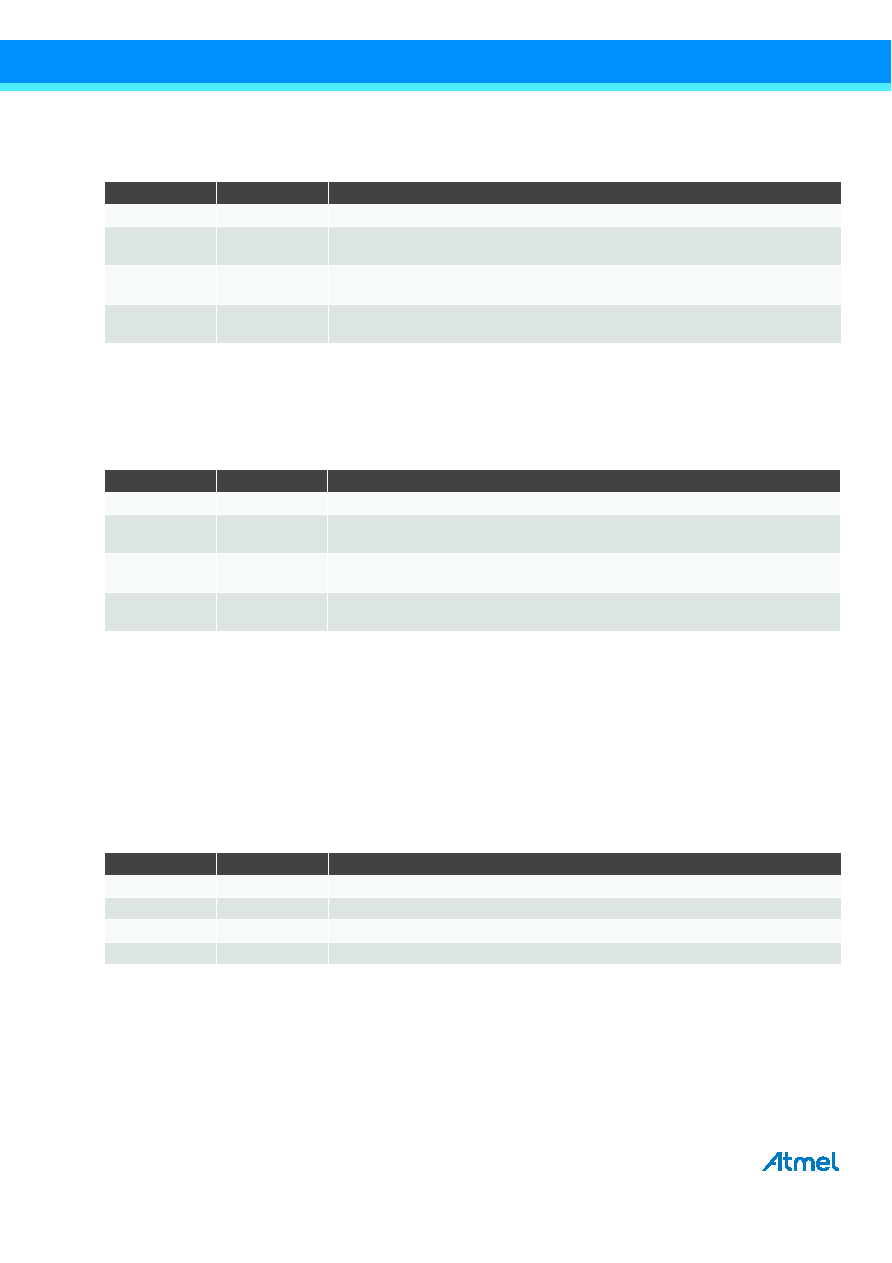

Table 15-3 shows the COM0A1:0 bit functionality when the WGM01:0 bits are set to fast PWM mode.

Table 15-4 shows the COM0A1:0 bit functionality when the WGM02:0 bits are set to phase correct PWM mode.

Bits 5:4 – COM0B1:0: Compare Match Output B Mode

These bits control the output compare pin (OC0B) behavior. If one or both of the COM0B1:0 bits are set, the OC0B output

overrides the normal port functionality of the I/O pin it is connected to. However, note that the data direction register (DDR)

bit corresponding to the OC0B pin must be set in order to enable the output driver.

When OC0B is connected to the pin, the function of the COM0B1:0 bits depends on the WGM02:0 bit setting.Table 15-5

shows the COM0B1:0 bit functionality when the WGM02:0 bits are set to a normal or CTC mode (non-PWM).

Table 15-3. Compare Output Mode, Fast PWM Mode(1)

COM0A1

COM0A0

Description

0

Normal port operation, OC0A disconnected.

0

1

WGM02 = 0: Normal port operation, OC0A disconnected.

WGM02 = 1: Toggle OC0A on compare match.

1

0

Clear OC0A on compare match, set OC0A at BOTTOM,

(non-inverting mode).

1

Set OC0A on compare match, clear OC0A at BOTTOM,

(inverting mode).

Note:

1.

A special case occurs when OCR0A equals TOP and COM0A1 is set. In this case, the compare match is

ignored, but the set or clear is done at BOTTOM. See Section 15.7.3 “Fast PWM Mode” on page 87 for more

details.

Table 15-4. Compare Output Mode, Phase Correct PWM Mode(1)

COM0A1

COM0A0

Description

0

Normal port operation, OC0A disconnected.

0

1

WGM02 = 0: Normal port operation, OC0A disconnected.

WGM02 = 1: Toggle OC0A on compare match.

1

0

Clear OC0A on compare match when up-counting. Set OC0A on compare match

when down-counting.

1

Set OC0A on compare match when up-counting. Clear OC0A on compare match

when down-counting.

Note:

1.

A special case occurs when OCR0A equals TOP and COM0A1 is set. In this case, the compare match is

ignored, but the set or clear is done at TOP. See Section 16.9.4 “Phase Correct PWM Mode” on page 111 for

more details.

Table 15-5. Compare Output Mode, non-PWM Mode

COM0B1

COM0B0

Description

0

Normal port operation, OC0B disconnected.

0

1

Toggle OC0B on compare match

1

0

Clear OC0B on compare match

1

Set OC0B on compare match

相关PDF资料 |

PDF描述 |

|---|---|

| MB9AF312NBGL | 32-BIT, FLASH, 40 MHz, RISC MICROCONTROLLER, PBGA112 |

| MB9BF506NBGL | 32-BIT, FLASH, 80 MHz, RISC MICROCONTROLLER, PBGA112 |

| MSP430G2333IRHB32 | 16-BIT, FLASH, 16 MHz, RISC MICROCONTROLLER, PQCC32 |

| M38003E6FS | 8-BIT, UVPROM, 8 MHz, MICROCONTROLLER, CQCC64 |

| M38802M2-XXXFS | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, CQCC64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MB9AF312KPMC1-G-JNE2 | 功能描述:ARM? Cortex?-M3 FM3 MB9A310K Microcontroller IC 32-Bit 40MHz 160KB (160K x 8) FLASH 52-LQFP (10x10) 制造商:cypress semiconductor corp 系列:FM3 MB9A310K 包装:托盘 零件状态:有效 核心处理器:ARM? Cortex?-M3 核心尺寸:32-位 速度:40MHz 连接性:CSIO,I2C,LIN,UART/USART,USB 外设:DMA,LVD,POR,PWM,WDT I/O 数:36 程序存储容量:160KB(160K x 8) 程序存储器类型:闪存 EEPROM 容量:- RAM 容量:16K x 8 电压 - 电源(Vcc/Vdd):2.7 V ~ 5.5 V 数据转换器:A/D 8x12b 振荡器类型:内部 工作温度:-40°C ~ 105°C(TA) 封装/外壳:52-LQFP 供应商器件封装:52-LQFP(10x10) 标准包装:160 |

| MB9AF312KPMC-ES-E1 | 制造商:FUJITSU 功能描述: |

| MB9AF312KPMC-G-JNE1 | 制造商:FUJITSU 功能描述: |

| MB9AF312KPMC-G-JNE2 | 功能描述:ARM? Cortex?-M3 FM3 MB9A310K Microcontroller IC 32-Bit 40MHz 160KB (160K x 8) FLASH 48-LQFP (7x7) 制造商:cypress semiconductor corp 系列:FM3 MB9A310K 包装:托盘 零件状态:有效 核心处理器:ARM? Cortex?-M3 核心尺寸:32-位 速度:40MHz 连接性:CSIO,I2C,LIN,UART/USART,USB 外设:DMA,LVD,POR,PWM,WDT I/O 数:36 程序存储容量:160KB(160K x 8) 程序存储器类型:闪存 EEPROM 容量:- RAM 容量:16K x 8 电压 - 电源(Vcc/Vdd):2.7 V ~ 5.5 V 数据转换器:A/D 8x12b 振荡器类型:内部 工作温度:-40°C ~ 105°C(TA) 封装/外壳:48-LQFP 供应商器件封装:48-LQFP(7x7) 标准包装:250 |

| MB9AF312KQN-ES-AWE2 | 制造商:FUJITSU 功能描述: |

发布紧急采购,3分钟左右您将得到回复。