- 您现在的位置:买卖IC网 > PDF目录378665 > MC74HC109D (MOTOROLA INC) Dual J-K Flip-Flop with Set and Reset PDF资料下载

参数资料

| 型号: | MC74HC109D |

| 厂商: | MOTOROLA INC |

| 元件分类: | 通用总线功能 |

| 英文描述: | Dual J-K Flip-Flop with Set and Reset |

| 中文描述: | HC/UH SERIES, DUAL POSITIVE EDGE TRIGGERED J-KBAR FLIP-FLOP, COMPLEMENTARY OUTPUT, PDSO16 |

| 封装: | PLASTIC, SOIC-16 |

| 文件页数: | 3/5页 |

| 文件大小: | 186K |

| 代理商: | MC74HC109D |

MC74HC109

High–Speed CMOS Logic Data

DL129 — Rev 6

3

MOTOROLA

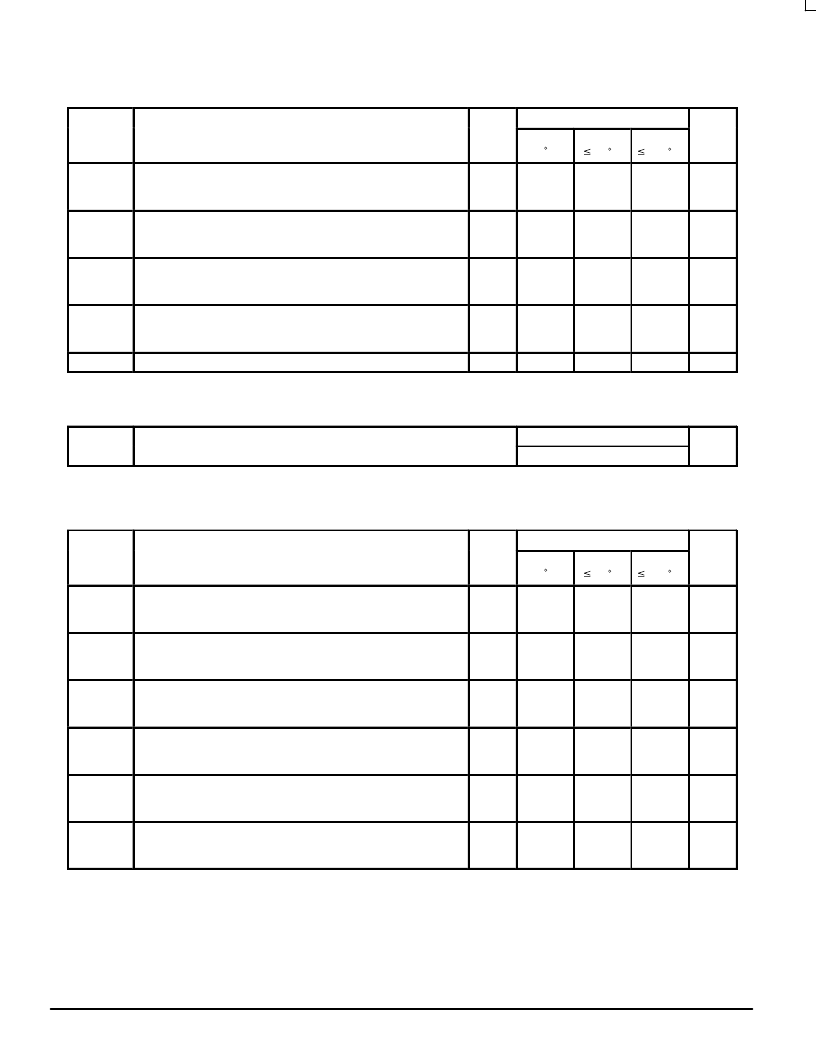

(Figures 1 and 4)

4.5

30

20

6.0

30

24

45

tPLH,

Maximum Propagation Delay, Set or Reset to Q or Q

2.0

230

290

37

345

ns

tTHL

(Figures 1 and 4)

4.5

15

22

1. For propagation delays with loads other than 50 pF, see Chapter 2 of the Motorola High–Speed CMOS Data Book (DL129/D).

2. Information on typical parametric values can be found in Chapter 2 of the Motorola High–Speed CMOS Data Book (DL129/D).

19

CPD

Power Dissipation Capacitance (Per Flip–Flop)*

* Used to determine the no–load dynamic power consumption: PD = CPD VCC2f + ICC VCC. For load considerations, see Chapter 2 of the

Motorola High–Speed CMOS Data Book (DL129/D).

Typical @ 25

°

C, VCC = 5.0 V

40

pF

Symbol

Parameter

V

25 C

125 C

tsu

Minimum Setup Time, J or K to Clock

2.0

100

85 C

125

150

Unit

ns

(Figure 3)

4.5

5

(Figure 2)

4.5

6.0

5

5

5

5

tw

Minimum Pulse Width, Set or Reset

2.0

6.0

80

14

100

5

5

120

20

5

5

ns

Minimum Pulse Width, Clock

(Figure 1)

2.0

4.5

80

16

100

17

120

24

ns

(Figure 1)

4.5

6.0

500

400

500

400

20

500

400

相关PDF资料 |

PDF描述 |

|---|---|

| MC74HC109N | Dual J-K Flip-Flop with Set and Reset |

| MC74HC10AD | Triple 3-Input NAND Gate |

| MC74HC10 | Triple 3-Input NAND Gate |

| MC74HC10ADT | Triple 3-Input NAND Gate |

| MC74HC10AN | Triple 3-Input NAND Gate |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC74HC109DR2 | 制造商:Motorola Inc 功能描述:HC/UH SERIES, DUAL POSITIVE EDGE TRIGGERED J-KBAR FLIP-FLOP, COMPLEMENTARY OUTPUT, PDSO16 |

| MC74HC109N | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC74HC109ND | 制造商:Motorola Inc 功能描述: |

| MC74HC10AD | 制造商:Motorola Inc 功能描述: |

| MC74HC10ADG | 功能描述:逻辑门 TRIPLE 3-IN AND GATE RoHS:否 制造商:Texas Instruments 产品:OR 逻辑系列:LVC 栅极数量:2 线路数量(输入/输出):2 / 1 高电平输出电流:- 16 mA 低电平输出电流:16 mA 传播延迟时间:3.8 ns 电源电压-最大:5.5 V 电源电压-最小:1.65 V 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:DCU-8 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。