- 您现在的位置:买卖IC网 > PDF目录29129 > MC88916DW80 (FREESCALE SEMICONDUCTOR INC) PLL BASED CLOCK DRIVER, 5 TRUE OUTPUT(S), 1 INVERTED OUTPUT(S), PDSO20 PDF资料下载

参数资料

| 型号: | MC88916DW80 |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | PLL BASED CLOCK DRIVER, 5 TRUE OUTPUT(S), 1 INVERTED OUTPUT(S), PDSO20 |

| 封装: | PLASTIC, SOIC-20 |

| 文件页数: | 2/9页 |

| 文件大小: | 260K |

| 代理商: | MC88916DW80 |

MC88916

MOTOROLA

TIMING SOLUTIONS

BR1333 — REV 5

2

19

20

18

17

16

15

14

13

12

11

2

1

3

4

5

6

7

8

9

10

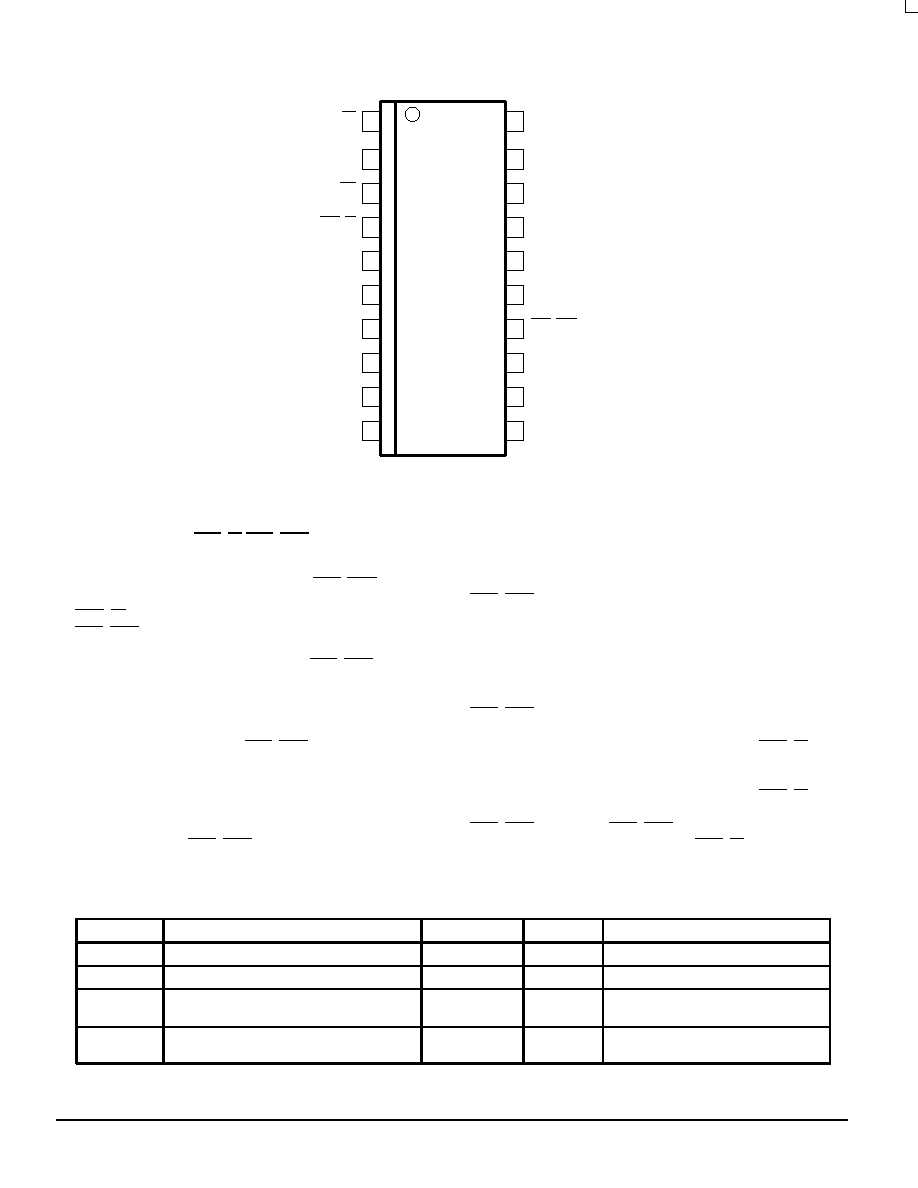

Pinout: 20–Lead Wide SOIC Package (Top View)

GND

Q3

2X_Q

VCC

Q/2

MR

VCC

RST_IN

Q2

VCC(AN)

GND

RC1

RST_OUT(LOCK)

GND(AN)

PLL_EN

SYNC

Q1

GND

VCC

Q0

Description of the RST_IN/RST_OUT(LOCK) Functionality (continued)

After the system start–up is complete and the 88916 is

phase–locked to the SYNC input signal (RST_OUT high), the

processor reset functionality can be utilized. When the

RST_IN pin is toggled low (min. pulse width=10nS),

RST_OUT(LOCK) will go to the low state and remain there

for 1024 cycles of the ‘Q’ output frequency (512 SYNC

cycles). During the time in which the RST_OUT(LOCK) is

actively pulled low, all the 88916 clock outputs will continue

operating correctly and in a locked condition to the SYNC

input (clock signals to the 68030/040 family of processors

must continue while the processor is in reset). A propagation

delay after the 1024th cycle RST_OUT(LOCK) goes back to

the high impedance state to be pulled high by the resistor.

Power Supply Ramp Rate Restriction for Correct 68030

Processor Reset Operation During System Start–up

Because the RST_OUT(LOCK) pin is an indicator of

phase–lock to the reference source, some constraints must

be placed on the power supply ramp rate to make sure the

RST_OUT(LOCK) signal holds the processor in reset during

system start–up (power–up). With the recommended loop

filter values (see Figure 7) the lock time is approximately

10ms. The phase–lock loop will begin attempting to lock to a

reference source (if it is present) when VCC reaches 2V. If

the VCC ramp rate is significantly slower than 10ms, then the

PLL could lock to the reference source, causing

RST_OUT(LOCK) to go high before the 88916 and 68030

processor is fully powered up, violating the processor reset

specification. Therefore, if it is necessary for the RST_IN pin

to be held high during power–up, the VCC ramp rate must be

less than 10mS for proper 68030/040 reset operation.

This ramp rate restriction can be ignored if the RST_IN pin

can be held low during system start–up (which holds

RST_OUT low). The RST_OUT(LOCK) pin will then be

pulled back high 1024 cycles after the RST_IN pin goes high.

CAPACITANCE AND POWER SPECIFICATIONS

Symbol

Parameter

Value Typ

Unit

Test Conditions

CIN

Input Capacitance

4.5

pF

VCC = 5.0V

CPD

Power Dissipation Capacitance

40

pF

VCC = 5.0V

PD1

Power Dissipation at 33MHz With 50

Thevenin Termination

15mW/Output

90mW/Device

mW

VCC = 5.0V

T = 25

°C

PD2

Power Dissipation at 33MHz With 50

Parallel Termination to GND

37.5mW/Output

225mW/Device

mW

VCC = 5.0V

T = 25

°C

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

..

.

相关PDF资料 |

PDF描述 |

|---|---|

| MDFLDM-TTL-450J | ACTIVE DELAY LINE, TRUE OUTPUT, DSO8 |

| MDFLDM-TTL-35G | ACTIVE DELAY LINE, TRUE OUTPUT, DSO8 |

| MDFLDM-TTL-100G | ACTIVE DELAY LINE, TRUE OUTPUT, DSO8 |

| MDFLDM-TTL-350T | ACTIVE DELAY LINE, TRUE OUTPUT, DSO8 |

| MDFLDM-TTL-175T | ACTIVE DELAY LINE, TRUE OUTPUT, DSO8 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC88916DWR2 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:LOW SKEW CMOS PLL CLOCK DRIVER WITH PROCESSOR RESET |

| MC88916EG70 | 功能描述:IC PLL CLOCK DRIVER 20-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| MC88916EG70R2 | 功能描述:IC PLL CLOCK DRIVER 20-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| MC88916EG80 | 功能描述:时钟驱动器及分配 FSL 5V CMOS PLL Clk Driver w/ Reset RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

| MC88916EG80R2 | 功能描述:时钟驱动器及分配 FSL 5V CMOS PLL Clk Driver w/ Reset RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。