- 您现在的位置:买卖IC网 > PDF目录45312 > MCF5484CVR200 (FREESCALE SEMICONDUCTOR INC) 32-BIT, 200 MHz, RISC PROCESSOR, PBGA388 PDF资料下载

参数资料

| 型号: | MCF5484CVR200 |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA388 |

| 封装: | 27 X 27 MM, 1 MM PITCH, MS-034AAL-1, PBGA-388 |

| 文件页数: | 11/34页 |

| 文件大小: | 602K |

| 代理商: | MCF5484CVR200 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页

SDRAM Bus

MCF548x ColdFire Microprocessor, Rev. 4

Freescale Semiconductor

19

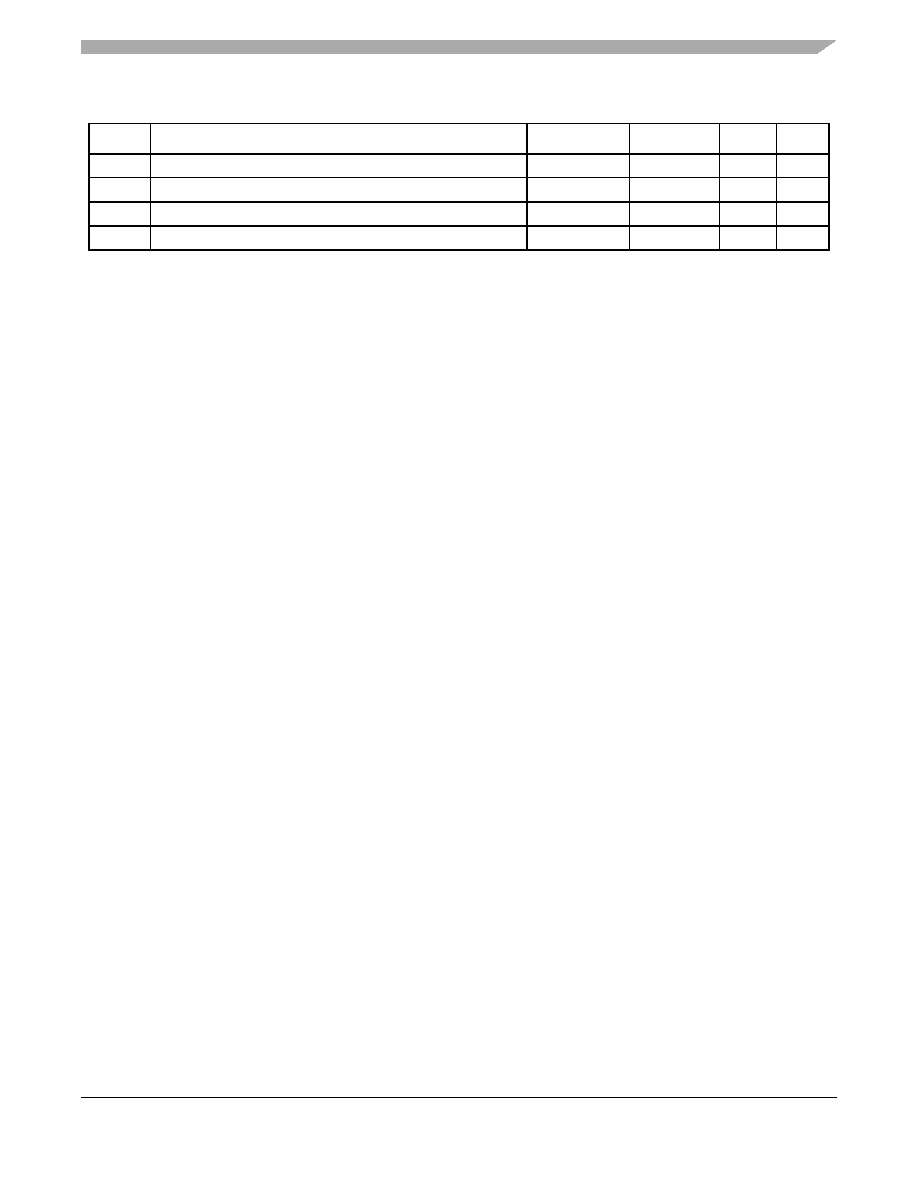

DD13

DQS input read preamble width (tRPRE)

0.9

1.1

SDCLK

DD14

DQS input read postamble width (tRPST)

0.4

0.6

SDCLK

DD15

DQS output write preamble width (tWPRE)0.25

—

SDCLK

DD16

DQS output write postamble width (tWPST)

0.4

0.6

SDCLK

1

DDR memories typically have a minimum speed specification of 83 MHz. Check memory component specifications to verify.

2 The frequency of operation is 2x or 4x the CLKIN frequency of operation. The MCF548X supports a single external

reference clock (CLKIN). This signal defines the frequency of operation for FlexBus and PCI, but SDRAM clock operates at

the same frequency as the internal bus clock. Please see the reset configuration signals description in the “Signal

Descriptions” chapter within the MCF548x Reference Manual.

3 SDCLK is one memory clock in (ns).

4 Pulse width high plus pulse width low cannot exceed max clock period.

5 Pulse width high plus pulse width low cannot exceed max clock period.

6 Command output valid should be 1/2 the memory bus clock (SDCLK) plus some minor adjustments for process,

temperature, and voltage variations.

7 This specification relates to the required input setup time of today’s DDR memories. SDDATA[31:24] is relative to SDDQS3,

SDDATA[23:16] is relative to SDDQS2, SDDATA[15:8] is relative to SDDQS1, and SDDATA[7:0] is relative SDDQS0.

8 The first data beat is valid before the first rising edge of SDDQS and after the SDDQS write preamble. The remaining data

beats is valid for each subsequent SDDQS edge.

9 This specification relates to the required hold time of today’s DDR memories. SDDATA[31:24] is relative to SDDQS3,

SDDATA[23:16] is relative to SDDQS2, SDDATA[15:8] is relative to SDDQS1, and SDDATA[7:0] is relative SDDQS0.

10 Data input skew is derived from each SDDQS clock edge. It begins with a SDDQS transition and ends when the last data

line becomes valid. This input skew must include DDR memory output skew and system level board skew (due to routing

or other factors).

11 Data input hold is derived from each SDDQS clock edge. It begins with a SDDQS transition and ends when the first data

line becomes invalid.

Table 13. DDR Timing Specifications (continued)

Symbol

Characteristic

Min

Max

Unit

Notes

相关PDF资料 |

PDF描述 |

|---|---|

| MCF5481CVR166 | 32-BIT, 166.66 MHz, RISC PROCESSOR, PBGA388 |

| MCF5483CZP166 | 32-BIT, 166.66 MHz, RISC PROCESSOR, PBGA388 |

| MCHC805PV8YDWR2 | 8-BIT, EEPROM, 4.2 MHz, MICROCONTROLLER, PDSO28 |

| MC68HC805PV8YDWR2 | 8-BIT, EEPROM, 4.2 MHz, MICROCONTROLLER, PDSO28 |

| MC68HC05PV8AYDWR3 | 8-BIT, MROM, 4.2 MHz, MICROCONTROLLER, PDSO28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MCF5484CVR200 | 制造商:Freescale Semiconductor 功能描述:Microprocessor IC |

| MCF5484CZP200 | 功能描述:微处理器 - MPU MCF548X V4ECORE MMU FPU RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| MCF5485 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:MCF548x ColdFire㈢ Microprocessor |

| MCF5485CVR200 | 功能描述:微处理器 - MPU MCF548X V4ECORE MMU FPU RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| MCF5485CZP200 | 功能描述:微处理器 - MPU MCF548X V4ECORE MMU FPU RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

发布紧急采购,3分钟左右您将得到回复。