- 您现在的位置:买卖IC网 > PDF目录67992 > MD82C237/B (INTERSIL CORP) 4 CHANNEL(S), 8 MHz, DMA CONTROLLER, CDIP40 PDF资料下载

参数资料

| 型号: | MD82C237/B |

| 厂商: | INTERSIL CORP |

| 元件分类: | DMA控制器 |

| 英文描述: | 4 CHANNEL(S), 8 MHz, DMA CONTROLLER, CDIP40 |

| 封装: | SIDE BRAZED, DIP-40 |

| 文件页数: | 7/25页 |

| 文件大小: | 508K |

| 代理商: | MD82C237/B |

162

82C237

Application Information

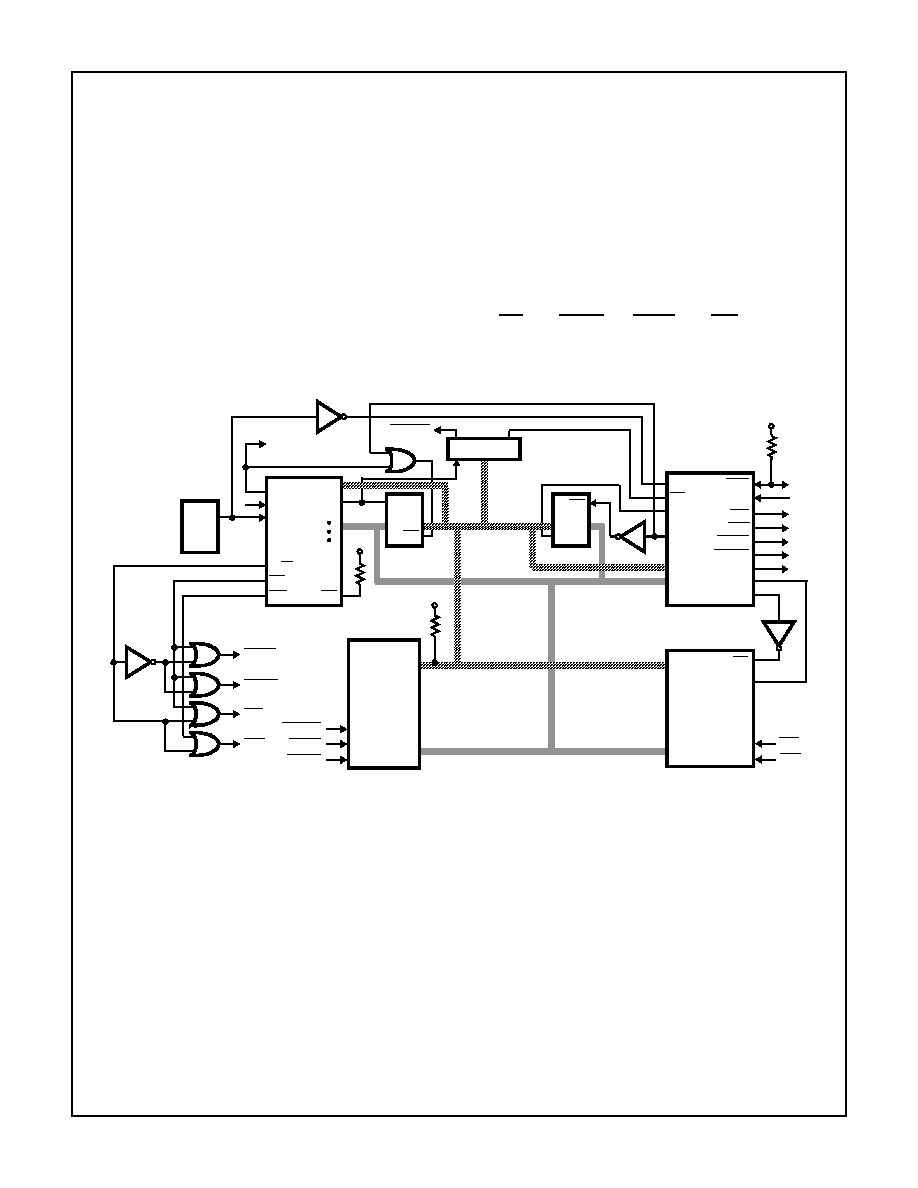

Figure 7 shows an application for a DMA system utilizing the

82C237 DMA controller and the 80C88 Microprocessor. In

this application, the 82C237 DMA controller is used to

improve system performance by allowing an I/O device to

transfer data directly to or from system memory.

Components

The system clock is generated by the 82C84A clock driver

and is inverted to meet the clock high and low times required

by the 82C237 DMA controller. The four OR gates are used

to support the 80C88 Microprocessor in minimum mode by

producing the control signals used by the processor to

access memory or I/O. A decoder is used to generate chip

select for the DMA controller and memory. The most signifi-

cant bits of the address are output on the address/data bus.

Therefore, the 82C82 octal latch is used to demultiplex the

address. Hold Acknowledge (HLDA) and Address Enable

(AEN) are “ORed” together to insure that the DMA controller

does not have bus contention with the microprocessor.

Operation

A DMA request (DREQ) is generated by the I/O device. After

receiving the DMA request, the DMA controller will issue a

Hold request (HRQ) to the processor. The system busses

are not released to the DMA controller until a Hold Acknowl-

edge signal is returned to the DMA controller from the 80C88

processor. After the Hold Acknowledge has been received,

addresses and control signals are generated by the DMA

controller to accomplish the DMA transfers. Data is trans-

ferred directly from the I/O device to memory (or vice versa)

with IOR and MEMW (or MEMR and IOW) being active.

Note that data is not read into or driven out of the DMA con-

troller in I/O-to-memory or memory-to-I/O data transfers.

FIGURE 7. APPLICATION FOR DMA SYSTEM

MEMR

MEMW

IOR

IOW

MEMCS

MEMR

MEMW

MEMORY

47K

VCC

ADDRESS BUS

DATA BUS

VCC

DATA BUS

80C88

WR

RD

M/IO

HRQ

HLDA

AX

ALE

AD0

AD7

MN/MX

CLK

82C84A

OR

82C85

HLDA

MEMCS

STB

82C82

OE

DECODER

ADDRESS BUS

STB

82C82

OE

A0-7

CS

CLK

EOP

HLDA

IOR

DACK

ADSTB

AEN

DB0-7

IOW

MEMR

MEMW

HRQ

DREQ0

82C237

IOR

IOW

VCC

CS

DREQ

I/O

DEVICE

NOTE: The address lines need pull-up resistors.

相关PDF资料 |

PDF描述 |

|---|---|

| MR82C237-12/B | 4 CHANNEL(S), 12.5 MHz, DMA CONTROLLER, CQCC44 |

| MD82C237-12/B | 4 CHANNEL(S), 12.5 MHz, DMA CONTROLLER, CDIP40 |

| MR82C237/B | 4 CHANNEL(S), 8 MHz, DMA CONTROLLER, CQCC44 |

| MD82C55A-5/883 | 24 I/O, PIA-GENERAL PURPOSE, CDIP40 |

| MD82C55A/883 | 24 I/O, PIA-GENERAL PURPOSE, CDIP40 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MD82C284-10 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:CPU System Clock Generator |

| MD82C284-10/883 | 制造商:Rochester Electronics LLC 功能描述:PERIPH CLK GENERATOR 5V 10MHZ 18CDIP /883 - Bulk |

| MD82C284-10/B | 制造商:Rochester Electronics LLC 功能描述: |

| MD82C284-12/883 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Clock Generator and Ready Interface for 80C286 Processors |

| MD82C284-6 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:CPU System Clock Generator |

发布紧急采购,3分钟左右您将得到回复。