- 您现在的位置:买卖IC网 > PDF目录68011 > MD82C54-12/B (INTERSIL CORP) 3 TIMER(S), PROGRAMMABLE TIMER, CDIP24 PDF资料下载

参数资料

| 型号: | MD82C54-12/B |

| 厂商: | INTERSIL CORP |

| 元件分类: | 时钟/数据恢复及定时提取 |

| 英文描述: | 3 TIMER(S), PROGRAMMABLE TIMER, CDIP24 |

| 封装: | CERDIP-24 |

| 文件页数: | 19/19页 |

| 文件大小: | 380K |

| 代理商: | MD82C54-12/B |

9

Both count and status of the selected counter(s) may be

latched simultaneously by setting both COUNT and STA-

TUS bits D5, D4 = 0. This is functionally the same as issuing

two separate read-back commands at once, and the above

discussions apply here also. Specifically, if multiple count

and/or status read-back commands are issued to the same

counter(s) without any intervening reads, all but the first are

ignored. This is illustrated in Figure 7.

If both count and status of a counter are latched, the first

read operation of that counter will return latched status,

regardless of which was latched first. The next one or two

reads (depending on whether the counter is programmed for

one or two type counts) return latched count. Subsequent

reads return unlatched count.

Mode Definitions

The following are defined for use in describing the operation

of the 82C54.

CLK PULSE:

A rising edge, then a falling edge, in that order, of a

Counter’s CLK input.

TRIGGER:

A rising edge of a Counter’s Gate input.

COUNTER LOADING:

The transfer of a count from the CR to the CE (See “Func-

tional Description”)

Mode 0: Interrupt on Terminal Count

Mode 0 is typically used for event counting. After the Control

Word is written, OUT is initially low, and will remain low until

the Counter reaches zero. OUT then goes high and remains

high until a new count or a new Mode 0 Control Word is writ-

ten to the Counter.

GATE = 1 enables counting; GATE = 0 disables counting.

GATE has no effect on OUT.

After the Control Word and initial count are written to a

Counter, the initial count will be loaded on the next CLK

pulse. This CLK pulse does not decrement the count, so for

an initial count of N, OUT does not go high until N + 1 CLK

pulses after the initial count is written.

If a new count is written to the Counter it will be loaded on

the next CLK pulse and counting will continue from the new

count. If a two-byte count is written, the following happens:

(1) Writing the first byte disables counting. Out is set low

immediately (no clock pulse required).

(2) Writing the second byte allows the new count to be

loaded on the next CLK pulse.

This allows the counting sequence to be synchronized by

software. Again OUT does not go high until N + 1 CLK

pulses after the new count of N is written.

If an initial count is written while GATE = 0, it will still be

loaded on the next CLK pulse. When GATE goes high, OUT

will go high N CLK pulses later; no CLK pulse is needed to

load the counter as this has already been done.

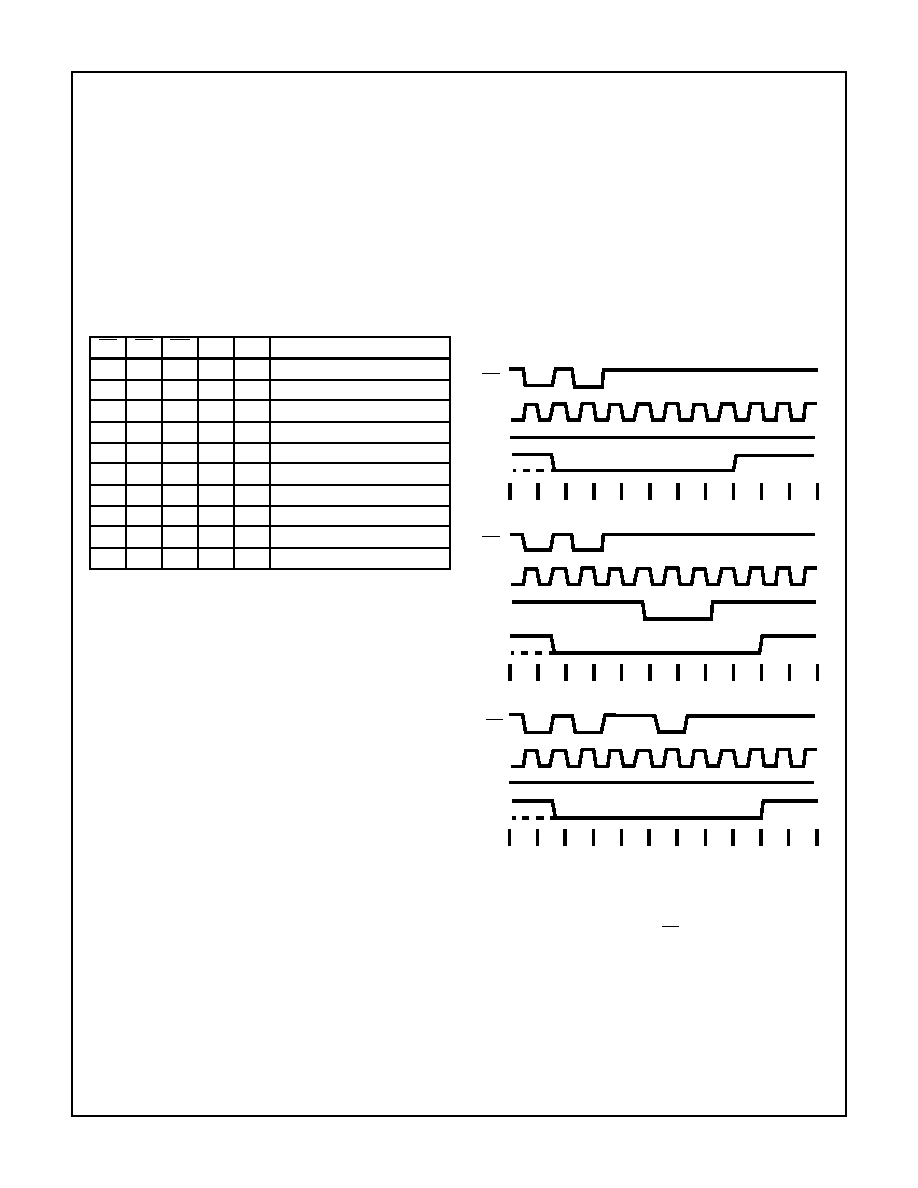

FIGURE 9. MODE 0

NOTES: The following conventions apply to all mode timing diagrams.

1. Counters are programmed for binary (not BCD) counting and for

reading/writing least significant byte (LSB) only.

2. The counter is always selected (CS always low).

3. CW stands for “Control Word”; CW = 10 means a control word of

10, Hex is written to the counter.

4. LSB stands for Least significant “byte” of count.

5. Numbers below diagrams are count values. The lower number is

the least significant byte. The upper number is the most signifi-

cant byte. Since the counter is programmed to read/write LSB

only, the most significant byte cannot be read.

6. N stands for an undefined count.

7. Vertical lines show transitions between count values.

CS

RD

WR

A1

A0

0

1

0

Write into Counter 0

0

1

0

1

Write into Counter 1

0

1

0

1

0

Write into Counter 2

0

1

0

1

Write Control Word

0

1

0

Read from Counter 0

0

1

0

1

Read from Counter 1

0

1

0

Read from Counter 2

0

1

No-Operation (Three-State)

1

XXXX

No-Operation (Three-State)

0

1

X

No-Operation (Three-State)

FIGURE 8. READ/WRITE OPERATIONS SUMMARY

CW = 10

LSB = 4

WR

CLK

GATE

OUT

WR

CLK

GATE

OUT

WR

CLK

GATE

OUT

CW = 10

LSB = 3

CW = 10

LSB = 3

LSB = 2

NN

0

4

0

3

0

2

0

1

0

FF

FE

NNN

N

0

3

0

2

0

2

0

2

0

1

0

FF

N

NNN

0

3

0

2

0

1

0

2

0

1

0

FF

82C54

相关PDF资料 |

PDF描述 |

|---|---|

| MR82C54/883 | 3 TIMER(S), PROGRAMMABLE TIMER, CQCC28 |

| MD82C54/883 | 3 TIMER(S), PROGRAMMABLE TIMER, CDIP24 |

| MR82C84A/883 | 25 MHz, PROC SPECIFIC CLOCK GENERATOR, CQCC20 |

| MR83C154DCXXX-12/883D | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CQCC44 |

| MQ83C154DCXXX-16/883D | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CQFP44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MD82C54B | 制造商: 功能描述: 制造商:undefined 功能描述: |

| MD82C54Q | 制造商: 功能描述: 制造商:undefined 功能描述: |

| MD82C55/R | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MD82C55A | 制造商:HARRIS 制造商全称:HARRIS 功能描述:CMOS Programmable Peripheral Interface |

| MD82C55A/B | 制造商:Intersil Corporation 功能描述:CMOS PROGRAMMABLE PERIPHERAL INTRFC 40CDIP - Rail/Tube |

发布紧急采购,3分钟左右您将得到回复。