- 您现在的位置:买卖IC网 > PDF目录371109 > MH8S64DBKG-8 (Mitsubishi Electric Corporation) 536870912-BIT (8388608 - WORD BY 64-BIT)SynchronousDRAM PDF资料下载

参数资料

| 型号: | MH8S64DBKG-8 |

| 厂商: | Mitsubishi Electric Corporation |

| 英文描述: | 536870912-BIT (8388608 - WORD BY 64-BIT)SynchronousDRAM |

| 中文描述: | 536870912位(8388608 -文字,64位)SynchronousDRAM |

| 文件页数: | 20/55页 |

| 文件大小: | 588K |

| 代理商: | MH8S64DBKG-8 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页

MH8S64PHC -7,-8,-10

536870912-BIT (8388608 - WORD BY 64-BIT)SynchronousDRAM

MITSUBISHI LSIs

( / 55 )

20

MITSUBISHI

ELECTRIC

9/ Dec. /1998

Preliminary Spec.

Some contents are subject to change without notice.

MIT-DS-0282-0.0

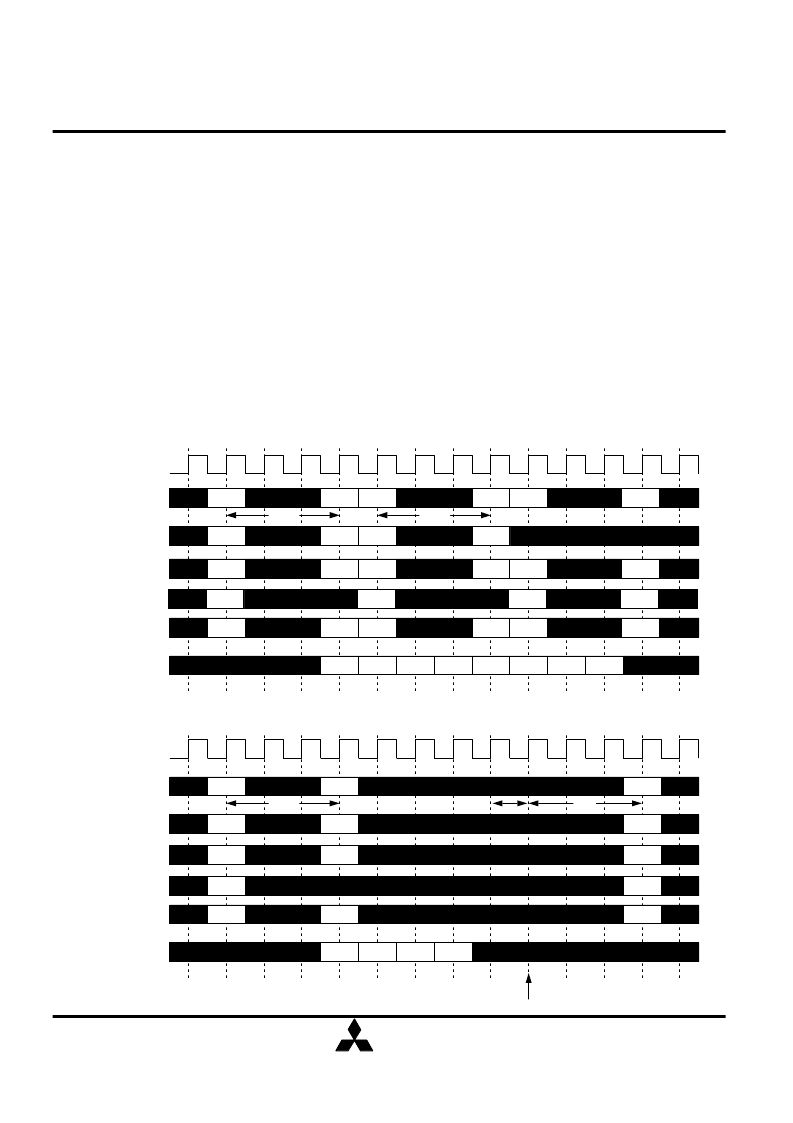

Multi Bank Interleaving WRITE (BL=4)

CK

Command

A10

DQ

ACT

Xa

Xa

00

Write

Y

0

00

Write

Y

0

10

Da0

Da1

Da2

Da3

ACT

Xb

Xb

10

PRE

0

00

tRCD

Db0

Db1

Db2

Db3

tRCD

CK

Command

A10

DQ

ACT

Xa

Xa

00

Write

Y

1

00

Da0

Da1

Da2

Da3

ACT

Xa

Xa

00

Internal precharge begins

tRCD

tRP

WRITE with Auto-Precharge (BL=4)

WRITE

After tRCD from the bank activation, a WRITE command can be issued. 1st input data is set

at the same cycle as the WRITE. Following(BL-1) data are written into the RAM, when the

Burst Length is BL. The start address is specified by A8-0, and the address sequence of burst

data is defined by the Burst Type. A WRITE command may be applied to any active bank, so

the row precharge time(tRP) can be hidden behind continuous input data by interleaving the

multiple banks. From the last input data to the PRE command, the write recovery time (tWR) is

required. When A10 is high at a WRITE command, the auto-precharge(WRITEA) is

performed. Any command(READ, WRITE, PRE, ACT) to the same bank is inhibited till the

internal precharge is complete. The internal precharge begins at tWR after the last input data

cycle. The next ACT command can be issued after tRP from the internal precharge timing.

The Mode Register can be WRITE command is issued and the remaining burst length is

ignored.The read data burst length os unaffected while in this mode.

A0-9

BA0,1

A0-9

BA0,1

A11

Xa

Xb

0

PRE

0

10

0

A11

Xa

Xa

tWR

相关PDF资料 |

PDF描述 |

|---|---|

| MH8S64DBKG-8L | 536870912-BIT (8388608 - WORD BY 64-BIT)SynchronousDRAM |

| MH8S72BAFD-8 | LJT 37C 37#22D PIN WALL RECP |

| MH8S72BAFD-7 | Circular Connector; No. of Contacts:37; Series:MS27467; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:15; Circular Contact Gender:Pin; Circular Shell Style:Straight Plug; Insert Arrangement:15-35 RoHS Compliant: No |

| MH8S72DCFD-6 | 603,979,776-BIT ( 8,388,608-WORD BY 72-BIT ) Synchronous DYNAMIC RAM |

| MH8S72PHC-10 | 603979776-BIT (8388608 - WORD BY 72-BIT)SynchronousDRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MH8S64DBKG-8L | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:536870912-BIT (8388608 - WORD BY 64-BIT)SynchronousDRAM |

| MH8S64FFC-10 | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:536870912-BIT (8388608 - WORD BY 64-BIT)SynchronousDRAM |

| MH8S64FFC-10L | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:536870912-BIT (8388608 - WORD BY 64-BIT)SynchronousDRAM |

| MH8S64PHC-10 | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:536870912-BIT (8388608 - WORD BY 64-BIT)SynchronousDRAM |

| MH8S64PHC-7 | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:536870912-BIT (8388608 - WORD BY 64-BIT)SynchronousDRAM |

发布紧急采购,3分钟左右您将得到回复。