- 您现在的位置:买卖IC网 > PDF目录45328 > MK1492-02RTRLF (INTEGRATED DEVICE TECHNOLOGY INC) 75 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 PDF资料下载

参数资料

| 型号: | MK1492-02RTRLF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 75 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 |

| 封装: | 0.150 INCH, SSOP-28 |

| 文件页数: | 4/7页 |

| 文件大小: | 70K |

| 代理商: | MK1492-02RTRLF |

MK1492-02

Intel Mobile/SDRAM Clock Source

MDS1492-02E

4

Revision 2028

Printed 2/2/98

MicroClock Division of ICS1271 Parkmoor Ave.San JoseCA95126(408)295-9800tel(408)295-9818fax

PRELIMINARY INFORMATION

ICRO

CLOCK

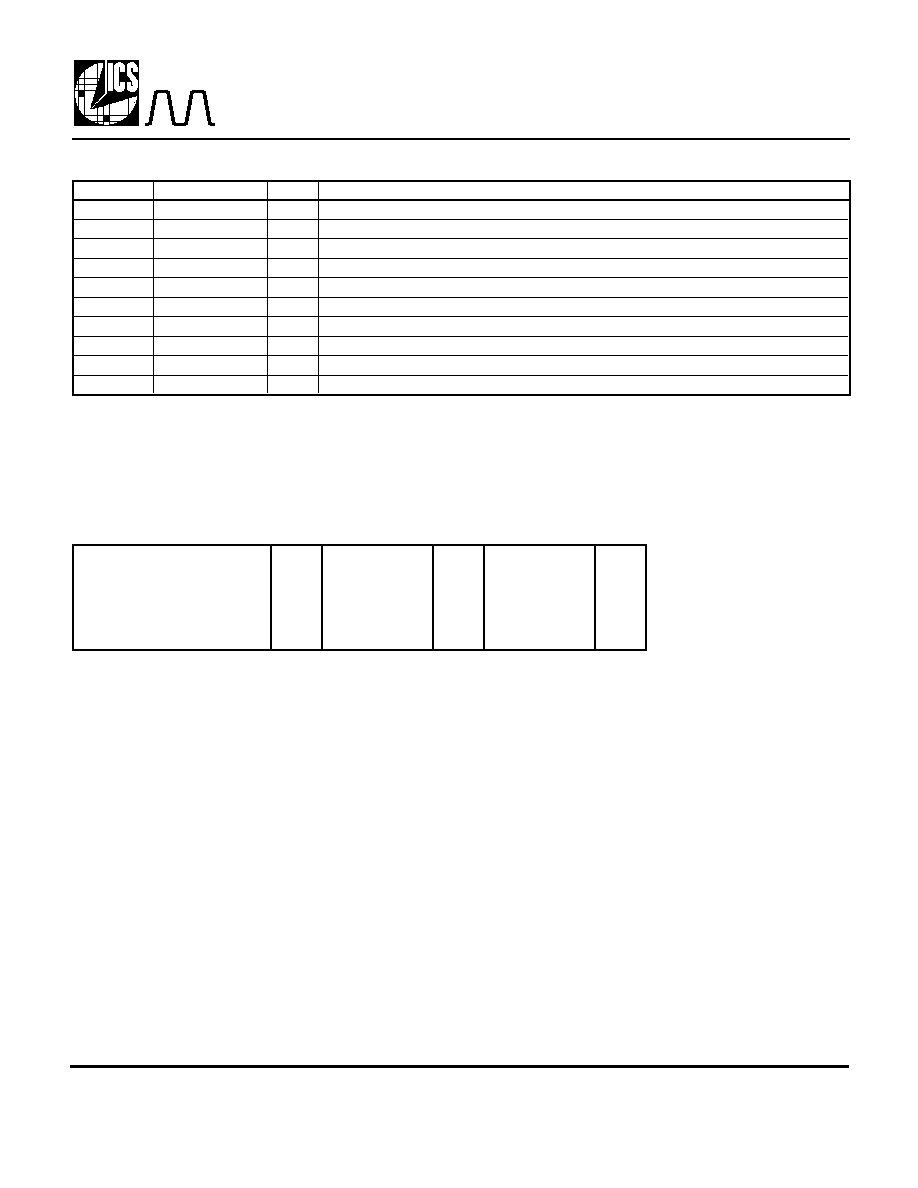

Power-On Default Conditions

Input Pin#

Function

Default Condition

5

OE

M

All outputs enabled.

15

CPUS#

1

HOST clocks running.

16

PCISTP#

1

PCI clocks running.

19

DS

1

HOST7, HOST8 disabled.

21

SEL0

1

48/24 (pin 21) set to 48 MHz

22

LE

1

Low EMI function OFF

24

FS

1

HOST frequency = 66.66 MHz.

25

SEL1

M

F1 (pin 28) set to 14.318 MHz

27

CSSS

1

Allows CPU STOP mode. Refer to Power Down Control Table on page 2.

28

PEN

M

PCI (pin 25) set to PCI clock (33.33 MHz). PCI (pin 24) set to PCIF clock (33.33 MHz).

General I 2C Serial Interface Operation

A. The I2C address for the MK1492-02 is D2(hex). For the clock generator to be addressed by an I2C

controller, this address must be sent as a start sequence, with an acknowledge bit between each byte as

shown below.

MK1492-02 Address (7 bits)

+ R/W# bit

8 bits dummy

ACK

Command code

ACK

Byte count

ACK

D2(hex)

Then Bytes 0, 1, 2, 3, 4, 5

in sequence unless a STOP

condition is encountered.

B. The MK1492-02 is an I2C slave component only. It does not have any read-back capability.

C. The data transfer rate supported by the MK1492-02 is 100K bits/sec (standard mode).

D. The input is operating at 3.3 V logic levels (refer to Electrical Specifications Table).

E. The data byte format is 8-bit bytes.

F. To simplify the I2C interface, the protocol is set to use only block writes from the controller. The bytes

must be accessed in sequential order from lowest to highest byte with the ability to stop after any

complete byte has been transferred. The Command code and Byte count shown above must be sent,

but the data is ignored for those two bytes. The data is loaded until a Stop condition is encountered.

G. In the power down mode (CPUS# Low), the SDATA and SCLK pins are tristated and the internal data

latches maintain all prior programming information.

H. At power-on, all registers are set to a default condition. See Byte 0 detail for its default condition;

Bytes 1 through 5 default to a 1 (Enabled output state).

相关PDF资料 |

PDF描述 |

|---|---|

| MK1492-02RLF | 75 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 |

| MK1492-04RTRLF | 75 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 |

| MK1492-04RTR | 75 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 |

| MK1492-04R | 75 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 |

| MK1493-01G | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MK1492-03R | 功能描述:时钟驱动器及分配 INTEL MOBILE/SDRAM CLOCK SOURCE RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

| MK1492-03RTR | 功能描述:IC CLK SRC MOBILE/SDRAM 28-QSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| MK1493-01 | 制造商:ICS 制造商全称:ICS 功能描述:PCI Clock Generator |

| MK1493-01G | 制造商:ICS 制造商全称:ICS 功能描述:PCI Clock Generator |

| MK1493-01GTR | 制造商:ICS 制造商全称:ICS 功能描述:PCI Clock Generator |

发布紧急采购,3分钟左右您将得到回复。