- 您现在的位置:买卖IC网 > PDF目录45328 > MK2049-02SI 51.84 MHz, OTHER CLOCK GENERATOR, PDSO20 PDF资料下载

参数资料

| 型号: | MK2049-02SI |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 51.84 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| 封装: | 0.300 INCH, SOIC-20 |

| 文件页数: | 11/11页 |

| 文件大小: | 136K |

| 代理商: | MK2049-02SI |

MK2049-02/03

Communications Clock PLLs

MDS 2049-02/03 C

9

Revision 091801

Integrated Circuit Systems, Inc. 525 Race Street San Jose CA 95126 (408)295-9800tel www.icst.com

External Components Selection

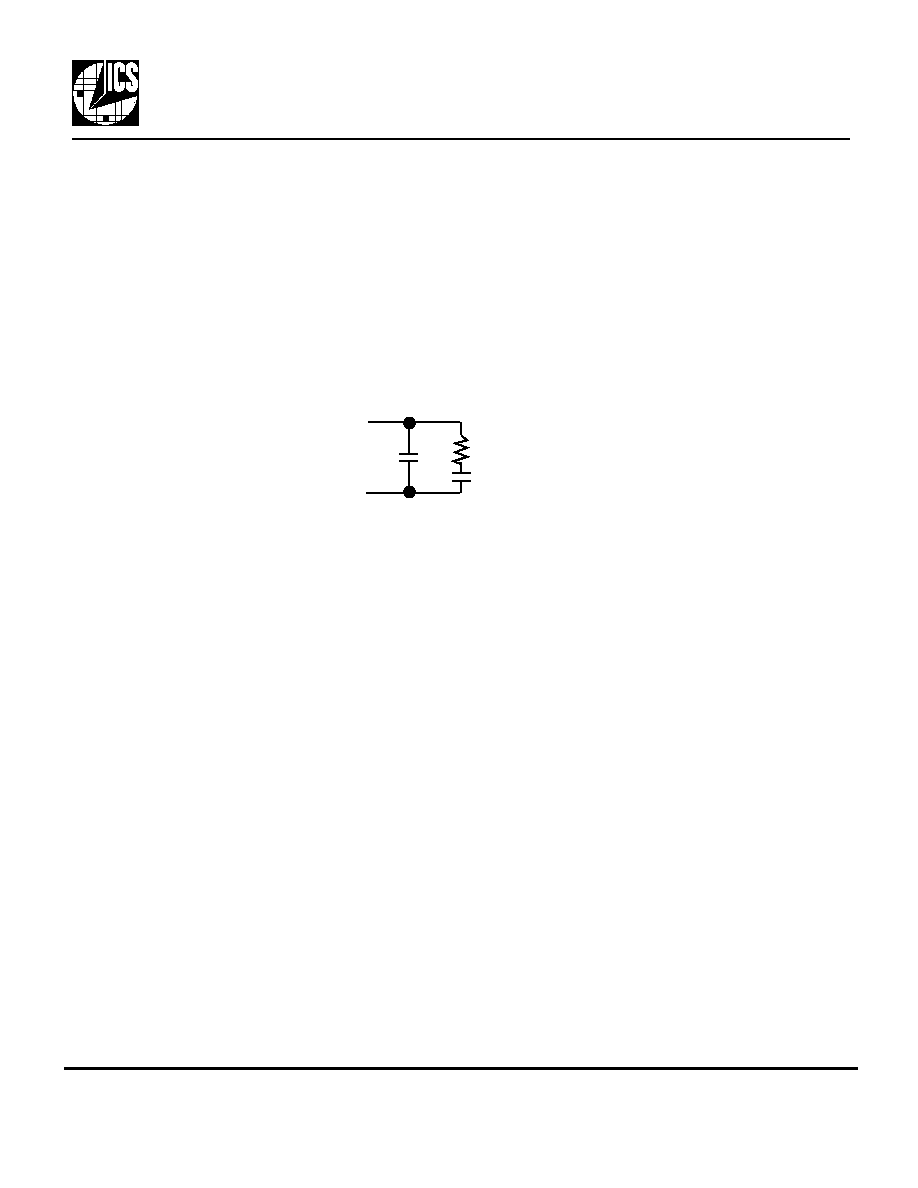

CAP2

CAP1

0.015

F

470 k

0.1 F

Crystal Operation

Figure 4. Loop Filter Component Values

Typical component values are shown. Contact the ICS applications department at

(408)297-1201 for the recommended values for your application.

The MK2049 operates by phase locking the input signal to a VCXO which consists of the special recommended

crystal and the integrated VCXO oscillator circuit on the MK2049. To achieve the best performance and reliability, the

layout guidelines shown on the previous page must be closely followed.

The frequency of oscillation of a quartz crystal is determined by its cut and by the load capacitors connected to it. The

MK2049 has variable load capacitors on-chip which “pull”, or change the frequency of the crystal. External stray

capacitance must be kept to a minimum to ensure maximum pullability of the crystal. To achieve this, the layout should

use short traces between the MK2049 and the crystal.

For the VCXO to operate correctly, a crystal properly specified and matched to the MK2049-02/03 must be used. For

more information, including a list of recommended crystals, refer to application note MAN05.

The external loop filter should be connected between CAP1 and CAP2 as shown in Figure 4 below, and as close to

the chip as possible. High quality ceramic capacitors are recommended. DO NOT use any type of polarized or

electrolytic capacitor. Ceramic capacitors should have C0G or NP0 dielectric. Another alternative is the Panasonic

PPS polymer dielectric series; their part number for the 0.1 F cap is ECHU1C104JB5. Avoid high-K dielectrics like

Z5U and X7R; these and other ceramics which have piezolectric properties allow mechanical vibration in the system

to increase the output jitter because the mechanical energy is converted directly to voltage noise on the VCO input.

LAYOUT AND EXTERNAL COMPONENTS (continued)

相关PDF资料 |

PDF描述 |

|---|---|

| MK2049-11SITR | 56 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| MK2049-11SITRLF | 56 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| MK2049-11SITRLF | 56 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| MK2049-11SI | 56 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| MK2049-45ASI | 125 MHz, OTHER CLOCK GENERATOR, PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MK2049-02SITR | 制造商:ICS 制造商全称:ICS 功能描述:Communications Clock PLLs |

| MK2049-02STR | 制造商:ICS 制造商全称:ICS 功能描述:Communications Clock PLLs |

| MK2049-03S | 制造商:MICROCLOCK 功能描述: |

| MK2049-03SI | 制造商:ICS 制造商全称:ICS 功能描述:Communications Clock PLLs |

| MK2049-03SITR | 制造商:ICS 制造商全称:ICS 功能描述:Communications Clock PLLs |

发布紧急采购,3分钟左右您将得到回复。