- 您现在的位置:买卖IC网 > PDF目录45328 > MK2049-03SI 49.152 MHz, OTHER CLOCK GENERATOR, PDSO20 PDF资料下载

参数资料

| 型号: | MK2049-03SI |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 49.152 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| 封装: | 0.300 INCH, SOIC-20 |

| 文件页数: | 7/11页 |

| 文件大小: | 136K |

| 代理商: | MK2049-03SI |

MK2049-02/03

Communications Clock PLLs

MDS 2049-02/03 C

5

Revision 091801

Integrated Circuit Systems, Inc. 525 Race Street San Jose CA 95126 (408)295-9800tel www.icst.com

OPERATING MODES

The MK2049-02/03 have three operating modes: External, Loop Timing, and Buffer. Although each mode uses an

input clock to generate various output clocks, there are important differences in their input and crystal requirements.

External Mode

The MK2049-02/03 accept an external 8 kHz clock and will produce a number of common communication clock

frequencies. The 8 kHz input clock does not need to have a 50% duty cycle; a “high” or “on” pulse as narrow as 10

ns is acceptable. In the MK2049-02, the rising edge of CLK2 is aligned with the rising edge of the 8 kHz ICLK; refer

to Figure 1 for more details. In the MK2049-03, the rising edges of CLK1 and CLK2 are both aligned with the rising

edge of the 8 kHz ICLK (unless noted in the shaded area of the table); refer to Figure 2 for more details.

Loop Timing Mode

This mode can be used to remove the jitter from standard high-frequency communication clocks. For T1 and E1

inputs, the CLK1 output will be the same as the input frequency, with CLK2 at twice the input frequency. For T3

0 = connect directly to ground, 1 = connect directly to VDD.

Crystal is connected to pins 2 and 3; clock input is applied to pin 13.

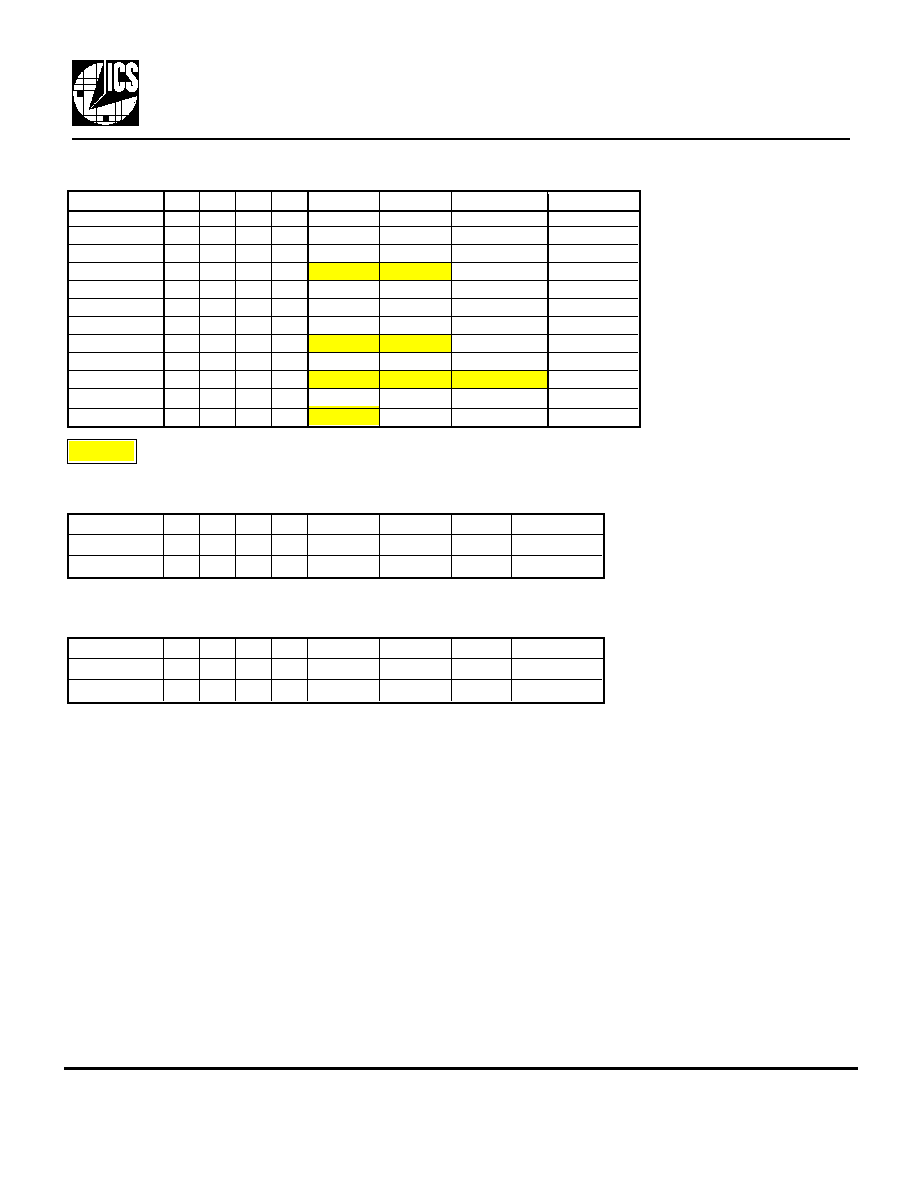

MK2049-03 Output Decoding Table – External Mode (MHz)

ICLK

FS3FS2FS1FS0

CLK1

CLK2

CLK3

Crystal

8 kHz

0

1.544

3.088

8 kHz

12.352

8 kHz

0

1

2.048

4.096

8 kHz

12.288

8 kHz

0

1

0

18.688

37.376

8 kHz

9.344

8 kHz

0

1

7.68

15.36

8 kHz

10.24

8 kHz

0

1

0

19.44

38.88

8 kHz

9.72

8 kHz

0

1

0

1

16.384

32.768

8 kHz

8.192

8 kHz

0

1

0

24.576

49.152

8 kHz

12.288

8 kHz

0

1

8.64

17.28

8 kHz

11.52

8 kHz

1

0

1

0

12.416

24.832

8 kHz

12.416

8 kHz

1

0

1

18.528

37.056

1.544 MHz

12.352

8 kHz

1

0

10.24

20.48

8 kHz

10.24

8 kHz

1

0

1

4.096

8.192

8 kHz

8.192

ICLK

FS3FS2 FS1FS0

CLK1

CLK2

Crystal

CLK3

1.544

1

0

1.544

3.088

12.352

N/A

2.048

1

0

1

2.048

4.096

12.288

N/A

MK2049-03 Output Decoding Table – Loop Timing Mode (MHz) for T1/E1

ICLK

FS3FS2 FS1FS0

CLK1

CLK2

Crystal

CLK3

19 - 28

1

0

ICLK/2

ICLK

ICLK/2

N/A

10 - 14

1

2*ICLK

4*ICLK

ICLK

Low

MK2049-03 Output Decoding Table – Buffer Mode (MHz)

= No Zero (Fixed) I/O Delay for these selections shown in the shaded boxes.

相关PDF资料 |

PDF描述 |

|---|---|

| MK2049-02SI | 51.84 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| MK2049-11SITR | 56 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| MK2049-11SITRLF | 56 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| MK2049-11SITRLF | 56 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| MK2049-11SI | 56 MHz, OTHER CLOCK GENERATOR, PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MK2049-03SITR | 制造商:ICS 制造商全称:ICS 功能描述:Communications Clock PLLs |

| MK2049-03STR | 制造商:ICS 制造商全称:ICS 功能描述:Communications Clock PLLs |

| MK2049-34 | 制造商:ICS 制造商全称:ICS 功能描述:3.3 V Communications Clock PLL |

| MK2049-34A | 制造商:ICS 制造商全称:ICS 功能描述:3.3 Volt Communications Clock VCXO PLL |

| MK2049-34SAI | 功能描述:IC VCXO PLL CLK SYNTH 20-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

发布紧急采购,3分钟左右您将得到回复。