- 您现在的位置:买卖IC网 > PDF目录45328 > MK2049-03SI 49.152 MHz, OTHER CLOCK GENERATOR, PDSO20 PDF资料下载

参数资料

| 型号: | MK2049-03SI |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 49.152 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| 封装: | 0.300 INCH, SOIC-20 |

| 文件页数: | 9/11页 |

| 文件大小: | 136K |

| 代理商: | MK2049-03SI |

MK2049-02/03

Communications Clock PLLs

MDS 2049-02/03 C

7

Revision 091801

Integrated Circuit Systems, Inc. 525 Race Street San Jose CA 95126 (408)295-9800tel www.icst.com

MK2049-03

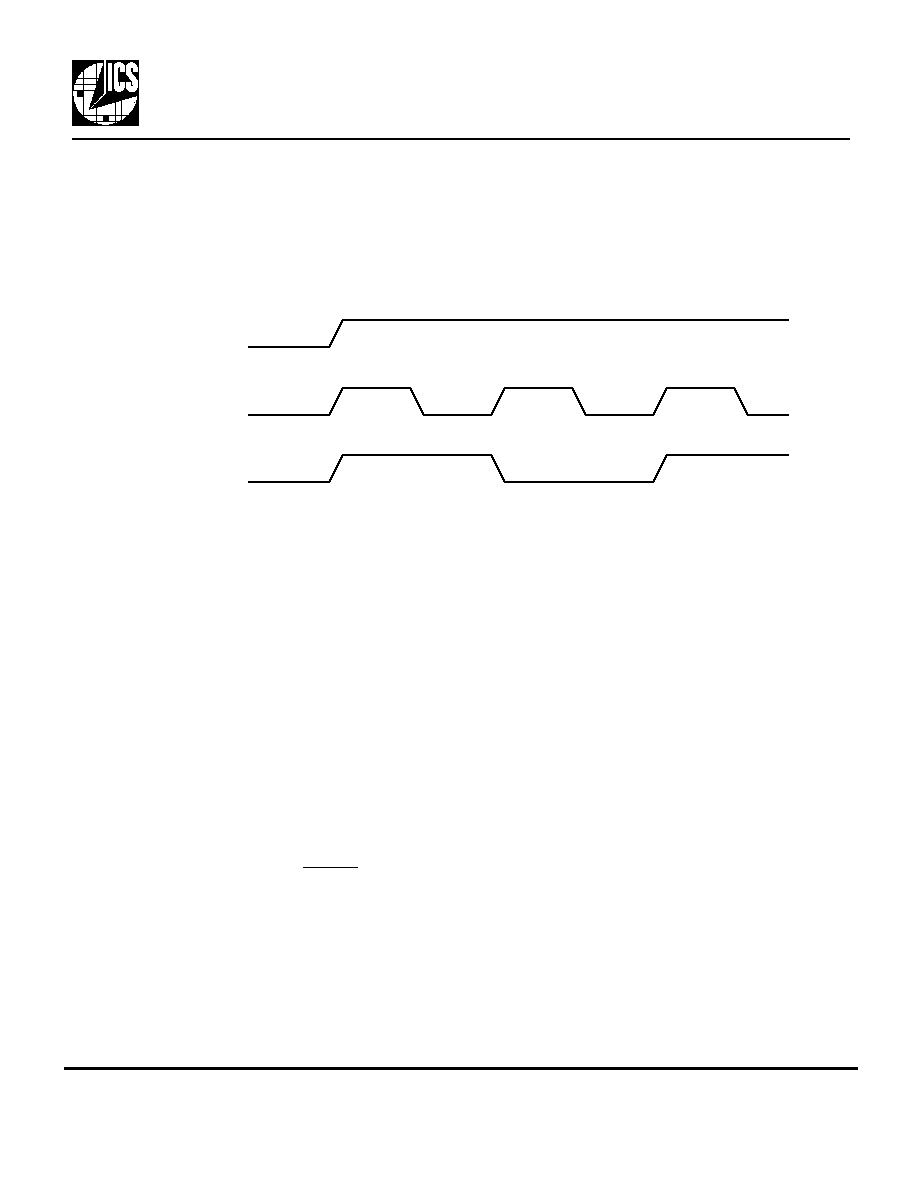

As illustrated in the diagram below, when using the MK2049-03 in one of the Zero Delay selections, the rising edge

of ICLK will be aligned with the rising edges of CLK1 and CLK2.

ICLK (8 kHz)

CLK2 (MHz)

CLK1 (MHz)

Figure 2. MK2049-03 Input and Output Clock Waveforms in Zero Delay Selections

In the MK2049-02 and MK2049-03 selections that are not Zero Delay, the phase relationship between the input and

output clocks is not predictable. Although it will not change once the MK2049-02/03 is running, this relationship is

likely to change when power is interrupted.

INPUT AND OUTPUT SYNCHRONIZATION (continued)

Measuring Zero Delay on the MK2049

The MK2049-02/03 both produce low-jitter output clocks. In addition, both parts have a very low bandwidth--on the

order of a few Hertz. Since most 8 kHz input clocks will have high jitter, this can make measuring the input-to-output

skew (zero delay feature) very difficult. The MK2049 are designed to reject the input jitter; when the input and

output clocks are both displayed on an oscilloscope, they may appear not to be locked because the scope trigger

point is constantly changing with the input jitter. In fact, the input and output clocks probably are locked, and the

MK2049 will have zero delay to the average position of the 8 kHz input clock. In order to see this clearly, a low jitter 8

kHz input clock is necessary. Most lab frequency sources are NOT SUITABLE for this since they have high jitter at

low frequencies.

Frequency Locking to the Input

In all modes, the output clocks are frequency-locked to the input. The output will remain at the specified output

frequency as long as the combined variation of the input frequency and the crystal does not exceed 100 ppm. For

example, if the crystal can vary ±40 ppm (initial accuracy + temperature + aging), then the input frequency can vary by

up to 60 ppm and still have the output clock remain frequency-locked.

相关PDF资料 |

PDF描述 |

|---|---|

| MK2049-02SI | 51.84 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| MK2049-11SITR | 56 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| MK2049-11SITRLF | 56 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| MK2049-11SITRLF | 56 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| MK2049-11SI | 56 MHz, OTHER CLOCK GENERATOR, PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MK2049-03SITR | 制造商:ICS 制造商全称:ICS 功能描述:Communications Clock PLLs |

| MK2049-03STR | 制造商:ICS 制造商全称:ICS 功能描述:Communications Clock PLLs |

| MK2049-34 | 制造商:ICS 制造商全称:ICS 功能描述:3.3 V Communications Clock PLL |

| MK2049-34A | 制造商:ICS 制造商全称:ICS 功能描述:3.3 Volt Communications Clock VCXO PLL |

| MK2049-34SAI | 功能描述:IC VCXO PLL CLK SYNTH 20-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

发布紧急采购,3分钟左右您将得到回复。