- 您现在的位置:买卖IC网 > PDF目录132985 > MK3727S 27 MHz, OTHER CLOCK GENERATOR, PDSO8 PDF资料下载

参数资料

| 型号: | MK3727S |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 27 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| 封装: | 0.150 INCH, SOIC-8 |

| 文件页数: | 1/7页 |

| 文件大小: | 136K |

| 代理商: | MK3727S |

MK3727

MDS 3727 L

1

Revision 091205

In te grat ed C i rc ui t Syst em s

5 25 Race Street, San Jose, CA 95 126

te l (40 8 ) 29 7-120 1

www.ics t.co m

LOW COST 24 TO 36 MHZ 3.3 VOLT VCXO

Description

The MK3727 series of devices include the original

MK3727S, and the new MK3727C and MK3727D. The

MK3727D and MK3727C are drop-in replacements for

the MK3727S device. Compared to these earlier

devices, the MK3727D and MK3727C offer a wider

operating frequency range and improved power supply

noise rejection. The MK3727D is recommended for

new designs.

The MK3727 series combines the functions of a VCXO

(Voltage Controlled Crystal Oscillator) and PLL (Phase

Locked Loop) frequency doubler onto a single chip.

Used in conjunction with an external pullable quartz

crystal, this monolithic integrated circuit replaces more

costly hybrid (canned) VCXO devices. The MK3727 is

designed primarily for data and clock recovery

applications within end products such as ADSL

modems, set-top box receivers, and telecom systems.

The MK3727D is recommended for new designs. The

MK3727D exhibits a moderate VCXO gain of

120ppm/V typical, when used with a high quality

external pullable quartz crystal. The MK3727C offers a

higher VCXO gain of 150ppm/V. The higher intrinsic

VCXO gain of the MK3727C may help compensate for

the reduced pullability of a low quality crystal used in

some applications. However, higher VCXO gain may

also increase clock output phase noise.

The frequency of the on-chip VCXO is adjusted by an

external control voltage input into pin VIN. Because

VIN is a high impedance input, it can be driven directly

from an PWM RC integrator circuit. Frequency output

increases with VIN voltage input. The usable range of

VIN is 0 to 3 V.

Features

MK3727D and MK3727C are drop-in upgrades to the

earlier MK3727S device

MK3727D and MK3727C offer 24 to 36 MHz output

frequency range (output frequency = 2x crystal

frequency) and improved power supply noise

rejection

Uses an inexpensive 12 to 18 MHz external crystal

Ideal for ADSL applications using 17.664 MHz

external pullable crystal to generate locked 35.328

MHz clock physical layer clock

Ideal for set-top box applications using 13.5 MHz

external pullable crystal to generate lock 27 MHz

clock transport video clock

On-chip VCXO with guaranteed pull range of ±115

ppm minimum (MK3727D)

VCXO input tuning voltage 0 to 3.3 V

Packaged in 8-pin SOIC (150 mil wide)

Available in Pb-free packaging

MK3727D is recommended for new designs.

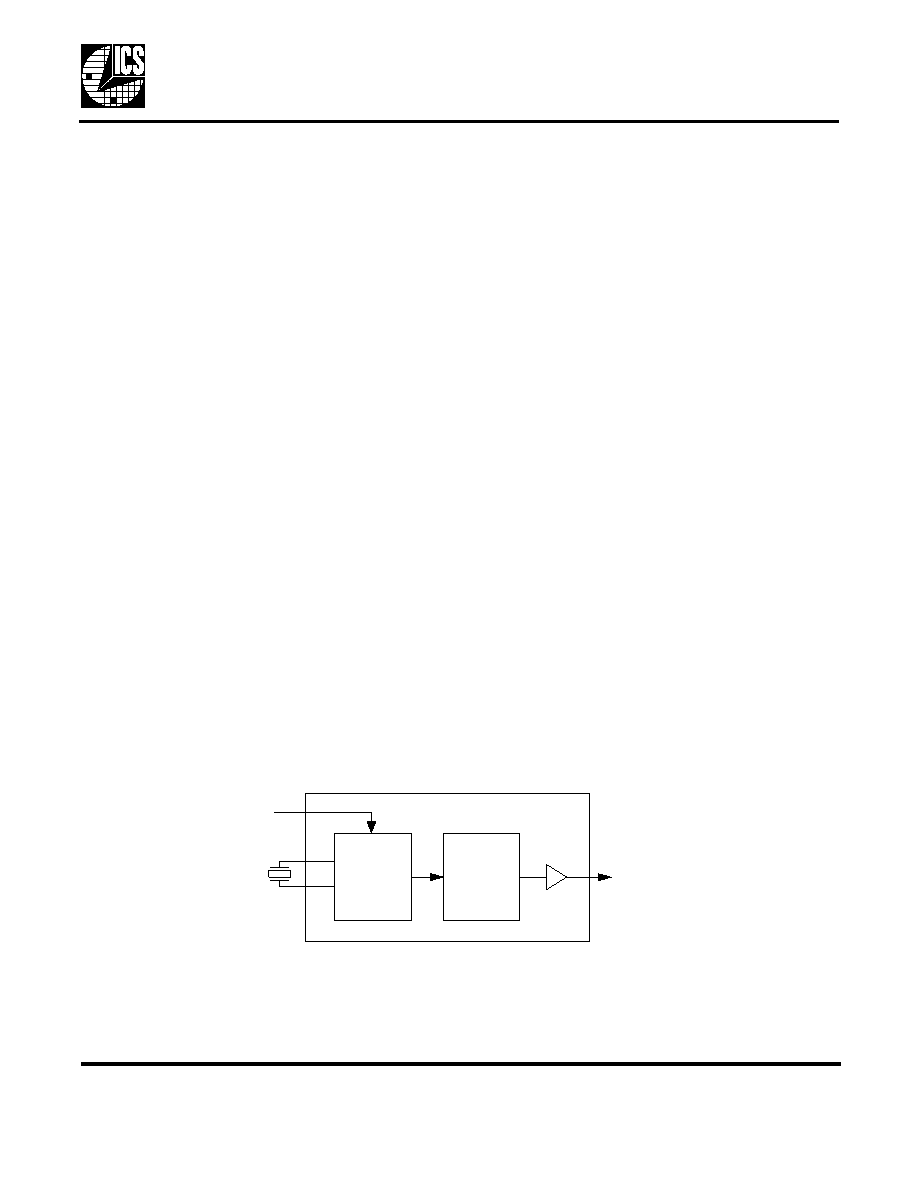

Block Diagram

24 to 36 M H z

(2 x C rysta l F re q u e n cy)

X1

X2

Volta g e

Co ntro lle d

Cry s ta l

Os c illa to r

PLL

Fre que nc y

D ouble r

VIN

1 2 to 1 8 M H z

P u lla b le

Crysta l

相关PDF资料 |

PDF描述 |

|---|---|

| MKI41T56N00 | 0 TIMER(S), REAL TIME CLOCK, PDIP8 |

| MKI41T56S00 | 0 TIMER(S), REAL TIME CLOCK, PDSO8 |

| M38223E4FP | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PQFP80 |

| MC68HC11E1CPB2 | 8-BIT, 2 MHz, MICROCONTROLLER, PQFP52 |

| MB95F166DPMC | 8-BIT, FLASH, 16.25 MHz, MICROCONTROLLER, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MK3727SLF | 制造商:Integrated Device Technology Inc 功能描述:IDT MK3727SLF PHASED LOCKED LOOP (PLL) - Rail/Tube 制造商:Integrated Device Technology Inc 功能描述:IDT MK3727SLF Phased Locked Loop (PLL) |

| MK3727STR | 制造商:INT_CIR_SYS 功能描述: |

| MK3732-05S | 制造商:MICROCLOCK 功能描述: 制造商:MICROCLOCK 功能描述:108 MHz, OTHER CLOCK GENERATOR, PDSO16 |

| MK3732-07 | 制造商:ICS 制造商全称:ICS 功能描述:ADSL VCXO CLOCK SOURCE |

| MK3732-07S | 制造商:ICS 制造商全称:ICS 功能描述:ADSL VCXO CLOCK SOURCE |

发布紧急采购,3分钟左右您将得到回复。