- 您现在的位置:买卖IC网 > PDF目录2014 > MPC93R51AC (IDT, Integrated Device Technology Inc)IC PLL CLK DRIVER LV 32-LQFP PDF资料下载

参数资料

| 型号: | MPC93R51AC |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 10/13页 |

| 文件大小: | 0K |

| 描述: | IC PLL CLK DRIVER LV 32-LQFP |

| 标准包装: | 250 |

| 类型: | PLL 时钟发生器 |

| PLL: | 带旁路 |

| 输入: | LVCMOS,LVPECL |

| 输出: | LVCMOS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:9 |

| 差分 - 输入:输出: | 是/无 |

| 频率 - 最大: | 240MHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-LQFP |

| 供应商设备封装: | 32-TQFP(7x7) |

| 包装: | 托盘 |

MPC93R51 REVISION 4 JANUARY 31, 2013

6

2013 Integrated Device Technology, Inc.

MPC93R51 Data Sheet

LOW VOLTAGE PLL CLOCK DRIVER

APPLICATIONS INFORMATION

Programming the MPC93R51

The MPC93R51 clock driver outputs can be configured

into several divider modes. In addition, the external feedback

of the device allows for flexibility in establishing various input

to output frequency relationships. The output divider of the

four output groups allows the user to configure the outputs

into 1:1, 2:1, 4:1 and 4:2:1 frequency ratios. The use of even

dividers ensure that the output duty cycle is always 50%.

Table 7 illustrates the various output configurations. The

table describes the outputs using the input clock frequency

CLK as a reference.

The output division settings establish the output

relationship. In addition, it must be ensured that the VCO will

be stable given the frequency of the outputs desired. The

feedback frequency should be used to situate the VCO into a

frequency range in which the PLL will be stable. The design

of the PLL supports output frequencies from 25 MHz to

240 MHz while the VCO frequency range is specified from

200 MHz to 480 MHz and should not be exceeded for stable

operation.

Using the MPC93R51 in Zero-Delay Applications

Nested clock trees are typical applications for the

MPC93R51. For these applications the MPC93R51 offers a

differential LVPECL clock input pair as a PLL reference. This

allows for the use of differential LVPECL primary clock

distribution devices such as the Freescale MC100EP111 or

MC10EP222, taking advantage of its superior low-skew

performance. Clock trees using LVPECL for clock distribution

and the MPC93R51 as LVCMOS PLL fanout buffer with zero

insertion delay will show significantly lower clock skew than

clock distributions developed from CMOS fanout buffers.

The external feedback option of the MPC93R51 PLL

allows for its use as a zero delay buffer. The PLL aligns the

feedback clock output edge with the clock input reference

edge and virtually eliminates the propagation delay through

the device.

The remaining insertion delay (skew error) of the

MPC93R51 in zero-delay applications is measured between

the reference clock input and any output. This effective delay

consists of the static phase offset (SPO or t()), I/O jitter

(tJIT(), phase or long-term jitter), feedback path delay and

the output-to-output skew (tSK(O) relative to the feedback

output.

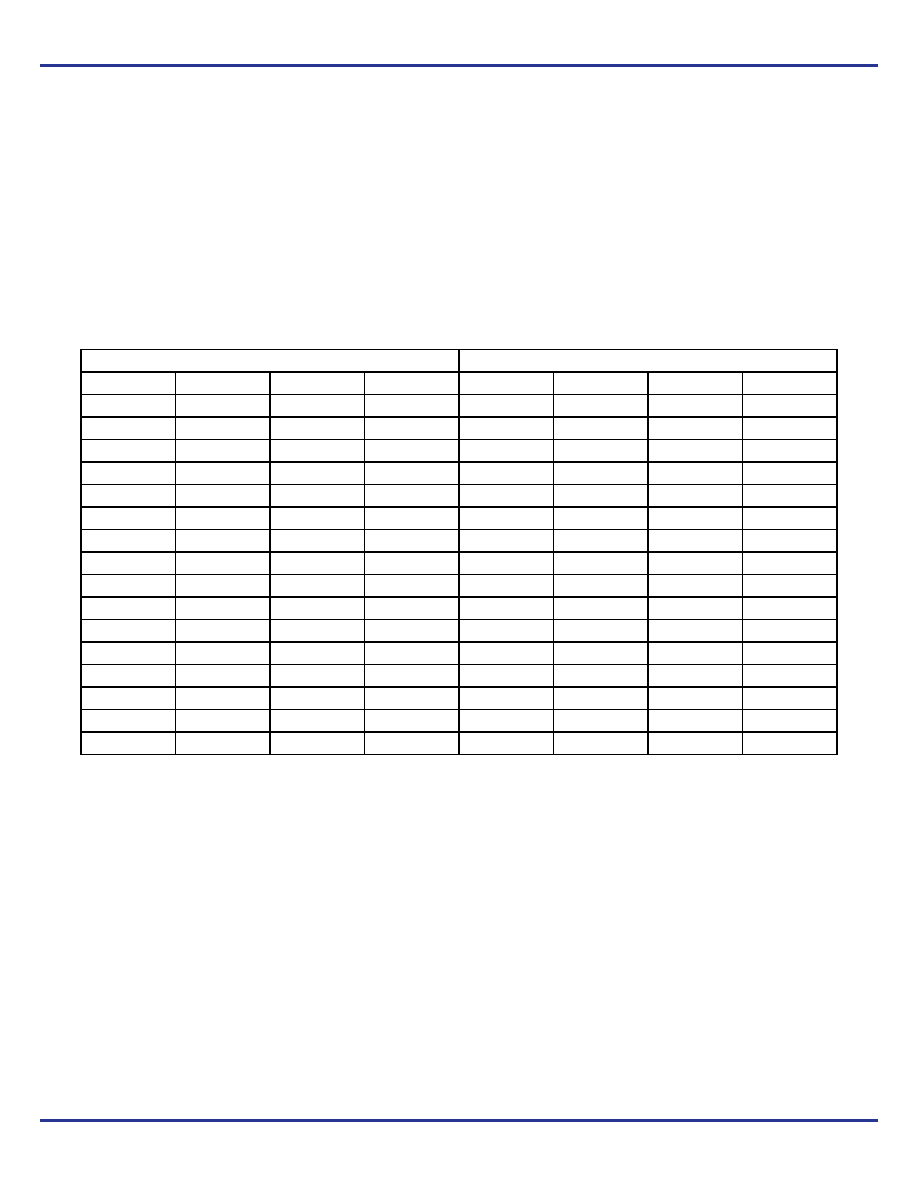

Table 7. Output Frequency Relationship(1) for an Example Configuration

1. Output frequency relationship with respect to input reference frequency CLK. QC1 is connected to EXT_FB.

Inputs

Outputs

FSELA

FSELB

FSELC

FSELD

QA

QB

QC

QD

0

2 * CLK

CLK

0

1

2 * CLK

CLK

2

0

1

0

4 * CLK

2 * CLK

CLK

2* CLK

0

1

4 * CLK

2 * CLK

CLK

0

1

0

2 * CLK

CLK

2

CLK

0

1

0

1

2 * CLK

CLK

2

CLK

2

0

1

0

4 * CLK

CLK

2 * CLK

0

1

4 * CLK

CLK

1

0

CLK

1

0

1

CLK

2

1

0

1

0

2 * CLK

CLK

2 * CLK

1

0

1

2 * CLK

CLK

1

0

CLK

2

CLK

1

0

1

CLK

2

CLK

2

1

0

2 * CLK

CLK

2 * CLK

1

2 * CLK

CLK

相关PDF资料 |

PDF描述 |

|---|---|

| MPC9608AC | IC CLOCK BUFFER ZD 1:10 32-LQFP |

| MPC962309EJ-1H | IC BUFFER ZD 1:5 3.3V 16-TSSOP |

| MPC96877VK | IC CLK DRIVER 1:10 SDRAM 52-BGA |

| MPC9773AE | IC PLL CLK GEN 1:12 3.3V 52-LQFP |

| MPC9850VF | IC PLL CLOCK GENERATOR 100MAPBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC93R51ACR2 | 功能描述:时钟发生器及支持产品 FSL 1-9 LVCMOS/LVPEC L to LVCMOS PLL Cloc RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MPC93R51D | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:LOW VOLTAGE PLL CLOCK DRIVER |

| MPC93R51FA | 功能描述:时钟驱动器及分配 3.3V 240MHz Clock Generator RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

| MPC93R51FAR2 | 制造商:Integrated Device Technology Inc 功能描述:PLL CLOCK DRVR SGL 32LQFP - Tape and Reel |

| MPC93R52 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:LOW VOLTAGE 3.3V LVCMOS 1:11 CLOCK GENERATOR |

发布紧急采购,3分钟左右您将得到回复。