- 您现在的位置:买卖IC网 > PDF目录29137 > MPC961PFA (FREESCALE SEMICONDUCTOR INC) 961 SERIES, PLL BASED CLOCK DRIVER, 17 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 PDF资料下载

参数资料

| 型号: | MPC961PFA |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 961 SERIES, PLL BASED CLOCK DRIVER, 17 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| 封装: | PLASTIC, LQFP-32 |

| 文件页数: | 5/9页 |

| 文件大小: | 162K |

| 代理商: | MPC961PFA |

MPC961P

496

FREESCALE SEMICONDUCTOR ADVANCED CLOCK DRIVERS DEVICE DATA

APPLICATIONS INFORMATION

Power Supply Filtering

The MPC961P is a mixed analog/digital product and as such

it exhibits some sensitivities that would not necessarily be seen

on a fully digital product. Analog circuitry is naturally susceptible

to random noise, especially if this noise is seen on the power

supply pins. The MPC961P provides separate power supplies

for the output buffers (VCC) and the phase-locked loop (VCCA)

of the device. The purpose of this design technique is to isolate

the high switching noise digital outputs from the relatively

sensitive internal analog phase-locked loop. In a controlled

environment such as an evaluation board this level of isolation

is sufficient. However, in a digital system environment where it

is more difficult to minimize noise on the power supplies, a

second level of isolation may be required. The simplest form of

isolation is a power supply filter on the VCCA pin for the

MPC961P.

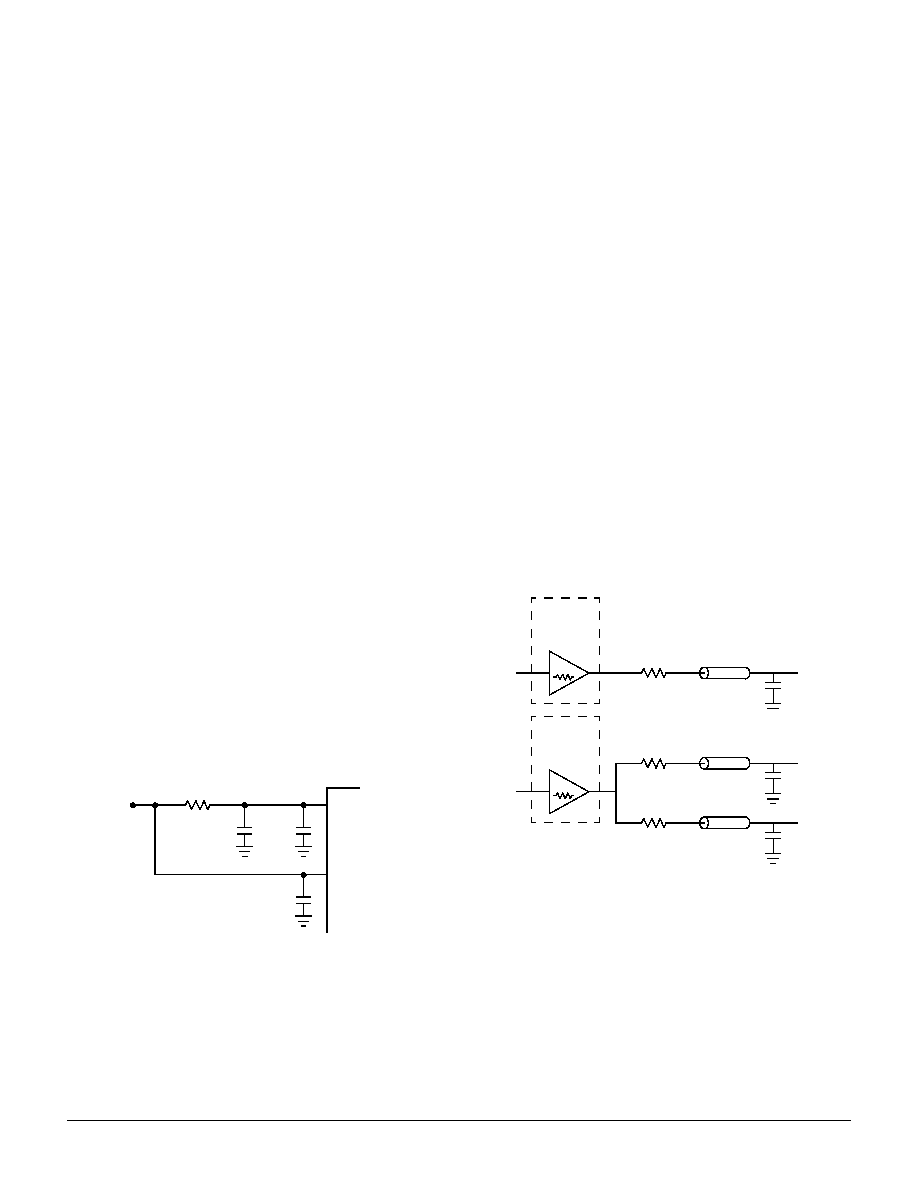

Figure 3 illustrates a typical power supply filter scheme. The

MPC961P is most susceptible to noise with spectral content in

the 10 kHz to 5 MHz range. Therefore the filter should be

designed to target this range. The key parameter that needs to

be met in the final filter design is the DC voltage drop that will

be seen between the VCC supply and the VCCA pin of the

MPC961P. From the data sheet the ICCA current (the current

sourced through the VCCA pin) is typically 2 mA

(5 mA maximum), assuming that a minimum of 2.375 V (VCC =

3.3 V or VCC = 2.5 V) must be maintained on the VCCA pin. The

(VCC = 3.3 V) or 5 to 15 (VCC = 2.5 V) to meet the voltage

drop criteria. The RC filter pictured will provide a broadband

filter with approximately 100:1 attenuation for noise whose

spectral content is above 20 kHz. As the noise frequency

crosses the series resonant point of an individual capacitor it's

overall impedance begins to look inductive and thus increases

with increasing frequency. The parallel capacitor combination

shown ensures that a low impedance path to ground exists for

frequencies well above the bandwidth of the PLL.

Figure 3. Power Supply Filter

Although the MPC961P has several design features to

minimize the susceptibility to power supply noise (isolated

power and grounds and fully differential PLL) there still may be

applications in which overall performance is being degraded

due to system power supply noise. The power supply filter

schemes discussed in this section should be adequate to

eliminate power supply noise related problems in most designs.

Driving Transmission Lines

The MPC961P clock driver was designed to drive high speed

signals in a terminated transmission line environment. To

provide the optimum flexibility to the user the output drivers

were designed to exhibit the lowest impedance possible. With

an output impedance of less than 15

the drivers can drive

either parallel or series terminated transmission lines. For more

information on transmission lines the reader is referred to

application note AN1091.

In most high performance clock networks point-to-point

distribution of signals is the method of choice. In a point-to-point

scheme either series terminated or parallel terminated

transmission lines can be used. The parallel technique

terminates the signal at the end of the line with a 50

resistance to VCC/2. This technique draws a fairly high level of

DC current and thus only a single terminated line can be driven

by each output of the MPC961P clock driver. For the series

terminated case however there is no DC current draw, thus the

outputs can drive multiple series terminated lines. Figure 4

illustrates an output driving a single series terminated line vs

two series terminated lines in parallel. When taken to its

extreme the fanout of the MPC961P clock driver is effectively

doubled due to its capability to drive multiple lines.

Figure 4. Single versus Dual Transmission Lines

The waveform plots of Figure 5 show the simulation results

of an output driving a single line vs two lines. In both cases the

drive capability of the MPC961P output buffer is more than

sufficient to drive 50

transmission lines on the incident edge.

Note from the delay measurements in the simulations a delta of

only 43 ps exists between the two differently loaded outputs.

This suggests that the dual line driving need not be used

exclusively to maintain the tight output-to-output skew of the

MPC961P. The output waveform in Figure 5 shows a step in the

waveform, this step is caused by the impedance mismatch seen

VCCA

VCC

MPC961P

10 nF

RF = 270 for VCC = 3.3 V

RF = 5–15 for VCC = 2.5 V

CF

33...100 nF

RF

VCC

14

IN

MPC961

OUTPUT

BUFFER

RS = 36

ZO = 50

OutA

14

IN

MPC961

OUTPUT

BUFFER

RS = 36

ZO = 50

OutB0

RS = 36

ZO = 50

OutB1

相关PDF资料 |

PDF描述 |

|---|---|

| MPC962308D-4R2 | 962308 SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| MPC962308D-2 | 962308 SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| MPC962308D-5H | 962308 SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| MPC962308D-3 | 962308 SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| MPC962308D-3R2 | 962308 SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC962305 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:Low-Cost 3.3 V Zero Delay Buffer |

| MPC962305D-1 | 功能描述:IC CLOCK BUFFER 1:5 8-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| MPC962305D-1H | 功能描述:IC CLOCK BUFFER 1:5 8-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| MPC962305D-1HR2 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:Low-Cost 3.3 V Zero Delay Buffer |

| MPC962305D-1R2 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:Low-Cost 3.3 V Zero Delay Buffer |

发布紧急采购,3分钟左右您将得到回复。