- 您现在的位置:买卖IC网 > PDF目录29137 > MPC962308D-2 (INTEGRATED DEVICE TECHNOLOGY INC) 962308 SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 PDF资料下载

参数资料

| 型号: | MPC962308D-2 |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 962308 SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| 封装: | 0.150 INCH, SOIC-16 |

| 文件页数: | 2/8页 |

| 文件大小: | 299K |

| 代理商: | MPC962308D-2 |

MPC962308

514

FREESCALE SEMICONDUCTOR ADVANCED CLOCK DRIVERS DEVICE DATA

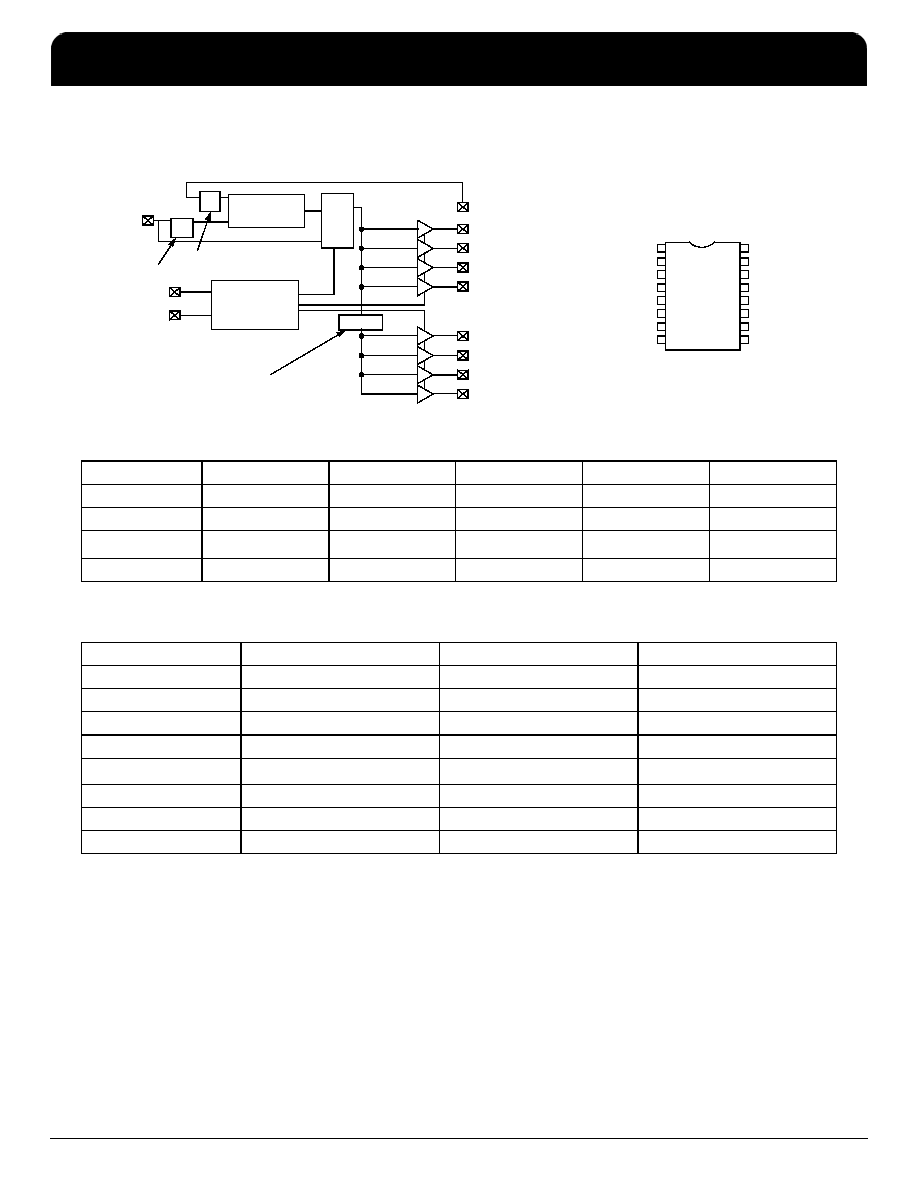

Table 10. Select Input Decoding

S2

S1

CLOCK A1—A4

CLOCK B1—B4

Output Source

PLL Shutdown

0

Three-State

PLL

Y

0

1

Driven

Three-State

PLL

N

10

Driven1

1. Outputs inverted on MPC962308-2 in bypass mode, S2=1 and S1=0.

Driven1

Reference

Y

1

Driven

PLL

N

Table 11. Available MPC962308 Configurations

Device

Feedback From

Bank A Frequency

Bank B Frequency

MPC962308-1

Bank A or Bank B

Reference

MPC962308-1H

Bank A or Bank B

Reference

MPC962308-2

Bank A

Reference

Reference/2

MPC962308-2

Bank B

2 X Reference

Reference

MPC962308-3

Bank A

2 X Reference

Reference or Reference[1]

1. Output phase is indeterminate (0

° or 180° from input clock). If phase integrity is required, use the MPC962308-2.

MPC962308-3

Bank B

4 X Reference

2 X Reference

MPC962308-4

Bank A or Bank B

2 X Reference

MPC962308-5H

Bank A or Bank B

Reference /2

SOIC/TSSOP

Top View

Pin Configuration

CLKA1

CLKA2

CLKA3

CLKA4

CLKB1

CLKB2

CLKB3

CLKB4

FBK

PLL

MUX

/2

Select Input

Decoding

/2

S2

S1

REF

Extra Divider (-3, -4)

Extra Divider (-5H)

Extra Divider (-2, -3)

Block Diagram

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

FBK

CLKA4

CLKA3

VDD

GND

CLKB4

CLKB3

S1

REF

CLKA1

CLKA2

VDD

GND

CLKB1

CLKB2

S2

MPC962308

3.3 V Zero Delay Buffer

NETCOM

IDT 3.3 V Zero Delay Buffer

Freescale Timing Solutions Organization has been acquired by Integrated Device Technology, Inc

MPC962308

2

相关PDF资料 |

PDF描述 |

|---|---|

| MPC962308D-5H | 962308 SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| MPC962308D-3 | 962308 SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| MPC962308D-3R2 | 962308 SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| MPC962308D-1 | 962308 SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| MPC962308D-2R2 | 962308 SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC962308D-2R2 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:3.3 V Zero Delay Buffer |

| MPC962308D-3 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:3.3 V Zero Delay Buffer |

| MPC962308D-3R2 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:3.3 V Zero Delay Buffer |

| MPC962308D-4 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:3.3 V Zero Delay Buffer |

| MPC962308D-4R2 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:3.3 V Zero Delay Buffer |

发布紧急采购,3分钟左右您将得到回复。