- 您现在的位置:买卖IC网 > PDF目录29137 > MPC9658ACR2 (FREESCALE SEMICONDUCTOR INC) 9658 SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 PDF资料下载

参数资料

| 型号: | MPC9658ACR2 |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 9658 SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| 封装: | 7 X 7 MM, LEAD FREE, LQFP-32 |

| 文件页数: | 8/12页 |

| 文件大小: | 344K |

| 代理商: | MPC9658ACR2 |

Advanced Clock Drivers Device Data

Freescale Semiconductor

5

MPC9658

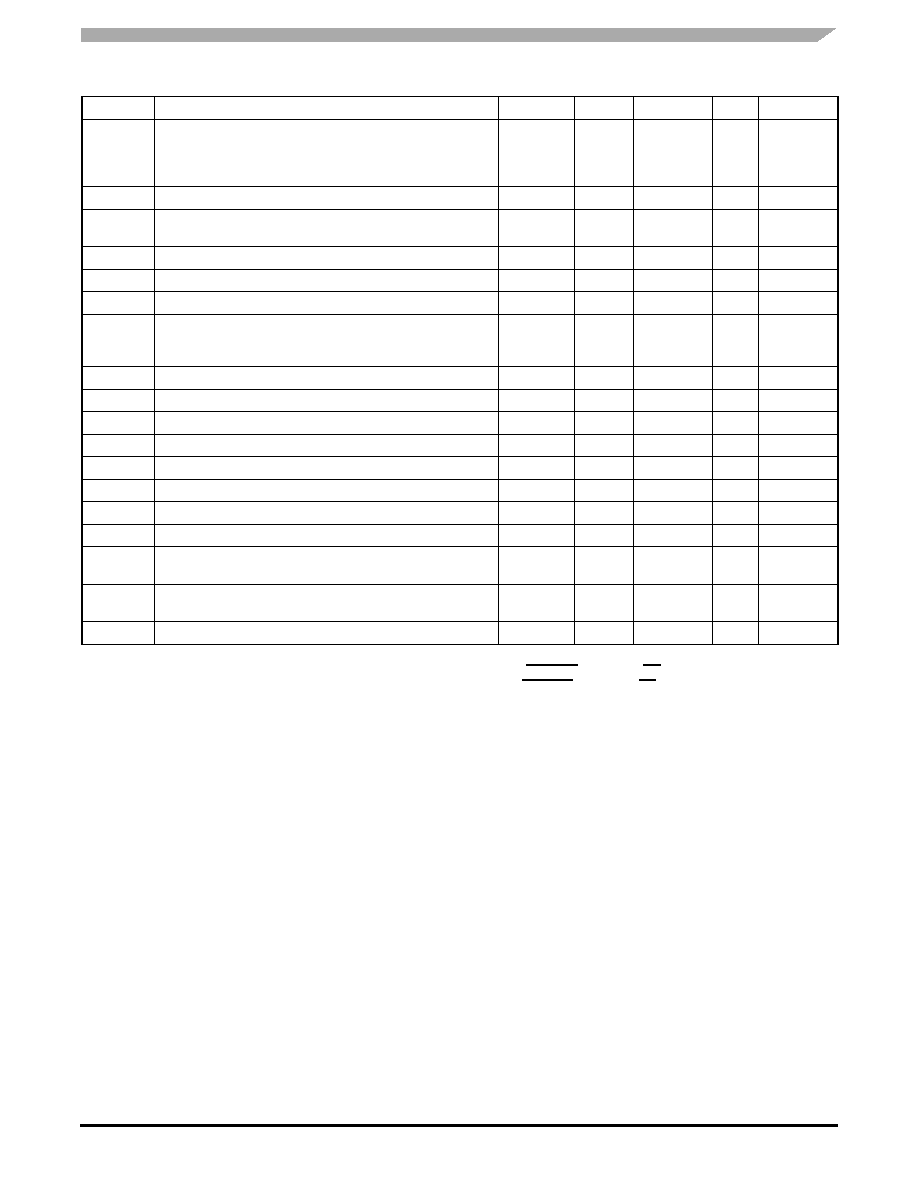

Table 6. AC Characteristics (VCC = 3.3 V ± 5%, TA = 0°C to 70°C)(1)

1. AC characteristics apply for parallel output termination of 50

to VTT.

Symbol

Characteristics

Min

Typ

Max

Unit

Condition

fREF

Input reference frequency

÷ 2 feedback(2)

PLL mode, external feedback

÷ 4 feedback(3)

Input reference frequency in PLL bypass mode(4)

2.

÷ 2 PLL feedback (high frequency range) requires VCO_SEL = 0, PLL_EN = 1, BYPASS = 1 and MR/OE =0.

3.

÷ 4 PLL feedback (low frequency range) requires VCO_SEL = 1, PLL_EN = 1, BYPASS = 1 and MR/OE =0.

4. In bypass mode, the MPC9658 divides the input reference clock.

100

50

0

250

125

250

MHz

PLL locked

fVCO

VCO lock frequency range(5)

5. The input frequency fREF must match the VCO frequency range divided by the feedback divider ratio FB: fREF =fVCO ÷ FB.

200

500

MHz

fMAX

Output Frequency

÷ 2 feedback(3)

÷ 4 feedback(4)

100

50

250

125

MHz

PLL locked

VPP

Peak-to-peak input voltage (PCLK)

500

1000

mV

LVPECL

VCMR(6)

6. VCMR (AC) is the crosspoint of the differential input signal. Normal AC operation is obtained when the crosspoint is within the VCMR range

and the input swing lies within the VPP (AC) specification. Violation of VCMR or VPP impacts static phase offset t().

Common Mode Range (PCLK)

1.2

VCC –0.9

V

LVPECL

tPW,MIN

Input Reference Pulse Width(7)

7. Calculation of reference duty cycle limits: DCREF,MIN = tPW,MIN fREF 100% and DCREF,MAX = 100% – DCREF,MIN.

2.0

ns

t()

Propagation Delay (static phase offset)

PCLK to FB_IN

fREF = 100 MHz

any frequency

–70

–125

+80

+125

ps

PLL locked

tPD

Propagation Delay (PLL and divider bypass)

PCLK to Q0-9

1.0

4.0

ns

tsk(O)

Output-to-output Skew(8)

8. Refer to APPLICATIONS INFORMATION for part-to-part skew calculation in PLL zero-delay mode.

120

ps

DC

Output Duty Cycle(9)

9. Output duty cycle is DC = (0.5 ± 400 ps

fOUT) 100%. For example, the DC range at fOUT = 100MHz is 46% < DC < 54%. T = output period.

(T

÷ 2)–400

T

÷ 2

(T

÷ 2)+400

ps

tr, tf

Output Rise/Fall Time

0.1

1.0

ns

0.55 to 2.4 V

tPLZ, HZ

Output Disable Time

7.0

ns

tPZL, LZ

Output Enable Time

6.0

ns

tJIT(CC)

Cycle-to-cycle jitter

80

ps

tJIT(PER)

Period Jitter

80

ps

tJIT()

I/O Phase Jitter fVCO = 500 MHz and ÷ 2 feedback, RMS (1σ)(10)

fVCO = 500 MHz and ÷ 4 feedback, RMS (1σ)

10. Refer to APPLICATIONS INFORMATION for a jitter calculation for other confidence factors than 1

σ and a characteristic for other VCO

frequencies.

5.5

6.5

ps

BW

PLL closed loop bandwidth(11)

÷ 2 feedback(3)

÷ 4 feedback(5)

11. –3 dB point of PLL transfer characteristics.

6 – 20

2 – 8

MHz

tLOCK

Maximum PLL Lock Time

10

ms

相关PDF资料 |

PDF描述 |

|---|---|

| MPC9658FA | 9658 SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| MPC9658ACR2 | 9658 SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| MPC973FA | 973 SERIES, PLL BASED CLOCK DRIVER, 12 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| MPC974FAR2 | 974 SERIES, PLL BASED CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| MPC974FA | 974 SERIES, PLL BASED CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC9658FA | 功能描述:时钟发生器及支持产品 2.5 3.3V 250MHz Clock Generator RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MPC9658FAR2 | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Driver Single 32-Pin LQFP T/R 制造商:Integrated Device Technology Inc 功能描述:MPC9658FAR2 - Tape and Reel |

| MPC96877VK | 功能描述:时钟发生器及支持产品 DDR2 PLL RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MPC96877VKR2 | 功能描述:时钟发生器及支持产品 DDR2 PLL RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MPC970 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:LOW VOLTAGE PLL CLOCK DRIVER |

发布紧急采购,3分钟左右您将得到回复。