- 您现在的位置:买卖IC网 > PDF目录80465 > MPC9855VFR2 (INTEGRATED DEVICE TECHNOLOGY INC) 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PBGA100 PDF资料下载

参数资料

| 型号: | MPC9855VFR2 |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PBGA100 |

| 封装: | 11 X 11 MM, 1 MM PITCH, MAPBGA-100 |

| 文件页数: | 8/12页 |

| 文件大小: | 260K |

| 代理商: | MPC9855VFR2 |

Advanced Clock Drivers Devices

Freescale Semiconductor

5

MPC9855

OPERATION INFORMATION

Output Frequency Configuration

The MPC9855 was designed to provide the commonly

used frequencies in PowerQUICC, PowerPC and other

microprocessor systems. Table 3 lists the configuration

values that will generate those common frequencies. The

MPC9855 can generate numerous other frequencies that

may be useful in specific applications. The output frequency

(fout) of either Bank A or Bank B may be calculated by the

following equation.

fout = 2000 / N

where fout is in MHz and N = 2 * CLK_x[0:5]

This calculation is valid for all values of N from 8 to 126.

Note that N = 15 is a modified case of the configuration inputs

CLK_x[0:5]. To achieve N = 15 CLK_x[0:5] is configured to

00111 or 7.

Crystal Input Operation

TBD

Power-Up and MR Operation

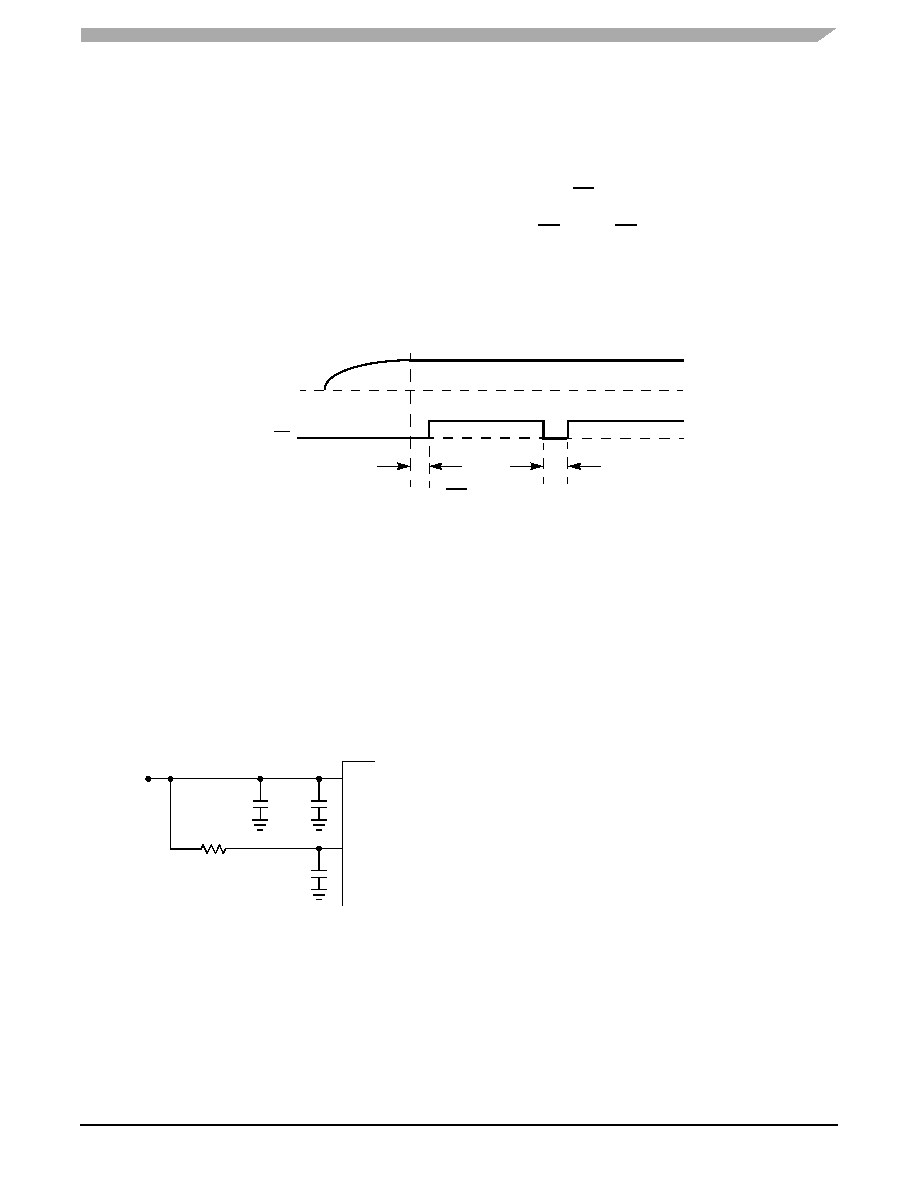

Figure 2 defines the release time and the minimum pulse

length for MR pin. The MR release time is based upon the

power supply being stable and within VDD specifications. See

Table 9 for actual parameter values. The MPC9855 may be

configured after release of reset and the outputs will be stable

for use after lock is obtained.

Figure 2. MR Operation

Power Supply Bypassing

The MPC9855 is a mixed analog/digital product. The

architecture of the MPC9855 supports low noise signal

operation at high frequencies. In order to maintain its superior

signal quality, all VDD pins should be bypassed by

high-frequency ceramic capacitors connected to GND. If the

spectral frequencies of the internally generated switching

noise on the supply pins cross the series resonant point of an

individual bypass capacitor, its overall impedance begins to

look inductive and thus increases with increasing frequency.

The parallel capacitor combination shown ensures that a low

impedance path to ground exists for frequencies well above

the noise bandwidth.

Figure 3. VCC Power Supply Bypass

Power Consumption Calculation

For unloaded outputs the power consumption of the

MPC9855 can be calculated as follows.

P = VDD * IDDBASE + nA * (VDDOA ** 2 * CPD * fA)

+ nB * (VDDOB ** 2 * CPD * fB)

where

VDD = core supply voltage

IDDBASE = base supply current

nA = number of A bank outputs (= 4)

nB = number of B bank outputs (= 4)

VDDOA = voltage supply on bank A outputs

VDDOB = voltage supply on bank B outputs

CPD = power dissipation capacitance

fA = frequency of bank A outputs

fB = frequency of bank B outputs

MR

VDD

treset_rel

treset_pulse

VDD

MPC9855

0.1

F

22

F

0.1

F

15

VDD

VDDA

相关PDF资料 |

PDF描述 |

|---|---|

| MC68HC08GR32AVFJE | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP32 |

| MC9S12C32PCPB16 | 16-BIT, FLASH, 16 MHz, MICROCONTROLLER, PQFP52 |

| MC9S12C32PVFA16 | 16-BIT, FLASH, 16 MHz, MICROCONTROLLER, PQFP48 |

| MCC68HC05L9D2 | 8-BIT, MROM, 2.45 MHz, MICROCONTROLLER, UUC128 |

| MPC8280CZQQLDX | 32-BIT, 333 MHz, RISC PROCESSOR, PBGA516 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC9855VM | 功能描述:时钟发生器及支持产品 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MPC9855VMR2 | 功能描述:时钟发生器及支持产品 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MPC9865VM | 功能描述:时钟发生器及支持产品 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MPC9865VMR2 | 功能描述:时钟发生器及支持产品 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MPC9893 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:Low Voltage PLL Intelligent Dynamic Clock (IDCS) Switch |

发布紧急采购,3分钟左右您将得到回复。