- 您现在的位置:买卖IC网 > PDF目录98046 > MTB75N03HDLT4 (ON SEMICONDUCTOR) 75 A, 25 V, 0.009 ohm, N-CHANNEL, Si, POWER, MOSFET PDF资料下载

参数资料

| 型号: | MTB75N03HDLT4 |

| 厂商: | ON SEMICONDUCTOR |

| 元件分类: | JFETs |

| 英文描述: | 75 A, 25 V, 0.009 ohm, N-CHANNEL, Si, POWER, MOSFET |

| 封装: | D2PAK-3 |

| 文件页数: | 11/12页 |

| 文件大小: | 256K |

| 代理商: | MTB75N03HDLT4 |

MTB75N03HDL

http://onsemi.com

8

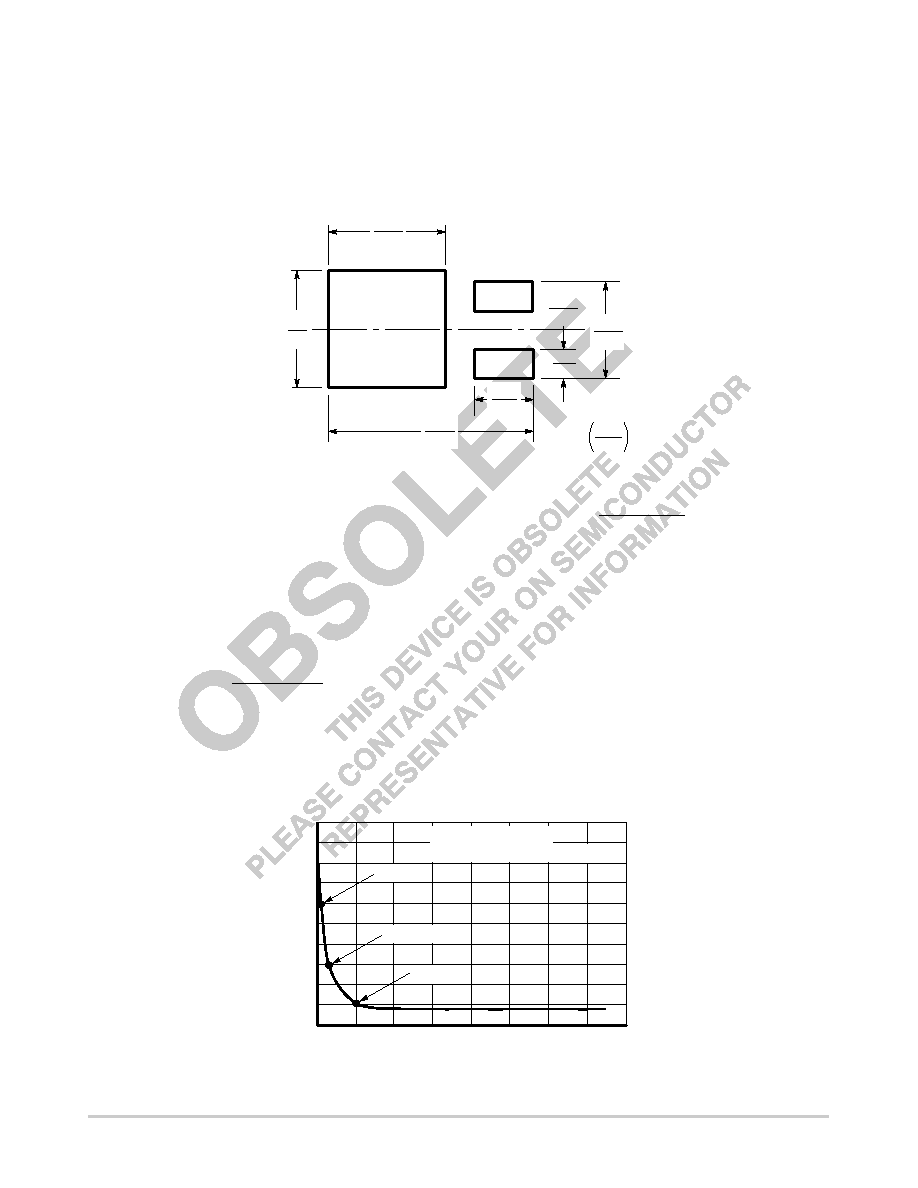

INFORMATION FOR USING THE D2PAK SURFACE MOUNT PACKAGE

RECOMMENDED FOOTPRINT FOR SURFACE MOUNTED APPLICATIONS

Surface mount board layout is a critical portion of the

total design. The footprint for the semiconductor packages

must be the correct size to ensure proper solder connection

interface between the board and the package. With the

correct pad geometry, the packages will self align when

subjected to a solder reflow process.

mm

inches

0.33

8.38

0.08

2.032

0.04

1.016

0.63

17.02

0.42

10.66

0.12

3.05

0.24

6.096

POWER DISSIPATION FOR A SURFACE MOUNT DEVICE

The power dissipation for a surface mount device is a

function of the drain pad size. These can vary from the

minimum pad size for soldering to a pad size given for

maximum power dissipation. Power dissipation for a

surface mount device is determined by TJ(max), the

maximum rated junction temperature of the die, RθJA, the

thermal resistance from the device junction to ambient, and

the operating temperature, TA. Using the values provided

on the data sheet, PD can be calculated as follows:

PD =

TJ(max) TA

RθJA

The values for the equation are found in the maximum

ratings table on the data sheet. Substituting these values

into the equation for an ambient temperature TA of 25°C,

one can calculate the power dissipation of the device. For a

D2PAK device, PD is calculated as follows.

PD =

150

°C 25°C

50

°C/W

= 2.5 Watts

The 50

°C/W for the D2PAK package assumes the use of

the recommended footprint on a glass epoxy printed circuit

board to achieve a power dissipation of 2.5 Watts. There are

other alternatives to achieving higher power dissipation

from the surface mount packages. One is to increase the

area of the drain pad. By increasing the area of the drain

pad, the power dissipation can be increased. Although one

can almost double the power dissipation with this method,

one will be giving up area on the printed circuit board

which can defeat the purpose of using surface mount

technology. For example, a graph of RθJA versus drain pad

area is shown in Figure 17.

Figure 16. Thermal Resistance versus Drain Pad

Area for the D2PAK Package (Typical)

A, AREA (SQUARE INCHES)

60

70

50

40

30

20

16

14

12

10

8

6

4

2

0

TO

AMBIENT

(

C/W)°

R

JA

,THERMAL

RESIST

ANCE,

JUNCTION

θ

5 Watts

3.5 Watts

2.5 Watts

Board Material = 0.0625″

G10/FR4, 2 oz Copper

TA = 25°C

相关PDF资料 |

PDF描述 |

|---|---|

| MTB75N06HDT4 | 75 A, 60 V, 0.01 ohm, N-CHANNEL, Si, POWER, MOSFET |

| MTB75N06HD | 75 A, 60 V, 0.01 ohm, N-CHANNEL, Si, POWER, MOSFET |

| MTB75N06HDT4 | 75 A, 60 V, 0.01 ohm, N-CHANNEL, Si, POWER, MOSFET |

| MTC-8301-CJ-I | 8-BIT, 10 MHz, RISC MICROCONTROLLER, CQCC44 |

| MTD1302T4 | 20 A, 30 V, 0.022 ohm, N-CHANNEL, Si, POWER, MOSFET |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MTB75N05HD | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:TMOS POWER FET 75 AMPERES 50 VOLTS |

| MTB75N05HDT4 | 功能描述:MOSFET N-CH 50V 75A D2PAK-3 RoHS:否 类别:分离式半导体产品 >> FET - 单 系列:- 标准包装:1,000 系列:MESH OVERLAY™ FET 型:MOSFET N 通道,金属氧化物 FET 特点:逻辑电平门 漏极至源极电压(Vdss):200V 电流 - 连续漏极(Id) @ 25° C:18A 开态Rds(最大)@ Id, Vgs @ 25° C:180 毫欧 @ 9A,10V Id 时的 Vgs(th)(最大):4V @ 250µA 闸电荷(Qg) @ Vgs:72nC @ 10V 输入电容 (Ciss) @ Vds:1560pF @ 25V 功率 - 最大:40W 安装类型:通孔 封装/外壳:TO-220-3 整包 供应商设备封装:TO-220FP 包装:管件 |

| MTB75N06 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:TMOS POWER FET 75 AMPERES 60 VOLTS |

| MTB75N06HD | 制造商:ON Semiconductor 功能描述:Trans MOSFET N-CH 60V 75A 3-Pin(2+Tab) D2PAK Rail |

| MTB7671 | 制造商:Megger 功能描述:METER TEST BOX |

发布紧急采购,3分钟左右您将得到回复。