- 您现在的位置:买卖IC网 > PDF目录98048 > MUN5137T3 (ON SEMICONDUCTOR) 100 mA, 50 V, PNP, Si, SMALL SIGNAL TRANSISTOR PDF资料下载

参数资料

| 型号: | MUN5137T3 |

| 厂商: | ON SEMICONDUCTOR |

| 元件分类: | 小信号晶体管 |

| 英文描述: | 100 mA, 50 V, PNP, Si, SMALL SIGNAL TRANSISTOR |

| 封装: | SC-70, 3 PIN |

| 文件页数: | 1/16页 |

| 文件大小: | 136K |

| 代理商: | MUN5137T3 |

Semiconductor Components Industries, LLC, 2001

January, 2001 – Rev. 4

1

Publication Order Number:

MUN5111T1/D

MUN5111T1 Series

Preferred Devices

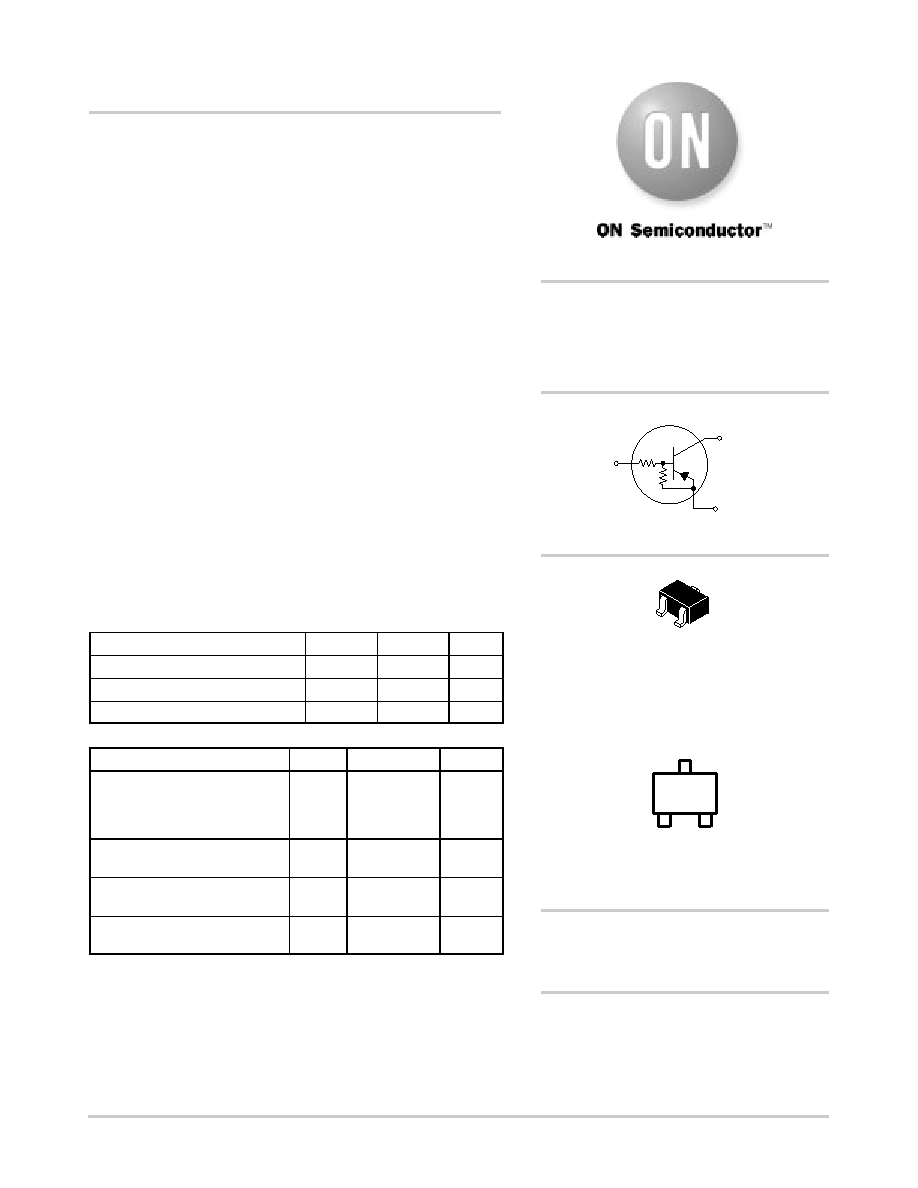

Bias Resistor Transistor

PNP Silicon Surface Mount Transistor

with Monolithic Bias Resistor Network

This new series of digital transistors is designed to replace a single

device and its external resistor bias network. The BRT (Bias Resistor

Transistor) contains a single transistor with a monolithic bias network

consisting of two resistors; a series base resistor and a base–emitter

resistor. The BRT eliminates these individual components by

integrating them into a single device. The use of a BRT can reduce

both system cost and board space. The device is housed in the

SC–70/SOT–323 package which is designed for low power surface

mount applications.

Simplifies Circuit Design

Reduces Board Space

Reduces Component Count

The SC–70/SOT–323 package can be soldered using wave or reflow.

The modified gull–winged leads absorb thermal stress during

soldering eliminating the possibility of damage to the die.

Available in 8 mm embossed tape and reel

Use the Device Number to order the 7 inch/3000 unit reel.

Replace “T1” with “T3” in the Device Number to order

the 13 inch/10,000 unit reel.

MAXIMUM RATINGS (TA = 25°C unless otherwise noted)

Rating

Symbol

Value

Unit

Collector-Base Voltage

VCBO

50

Vdc

Collector-Emitter Voltage

VCEO

50

Vdc

Collector Current

IC

100

mAdc

THERMAL CHARACTERISTICS

Characteristic

Symbol

Max

Unit

Total Device Dissipation

TA = 25°C

Derate above 25

°C

PD

202 (Note 1.)

310 (Note 2.)

1.6 (Note 1.)

2.5 (Note 2.)

mW

°C/W

Thermal Resistance –

Junction-to-Ambient

RθJA

618 (Note 1.)

403 (Note 2.)

°C/W

Thermal Resistance –

Junction-to-Lead

RθJL

280 (Note 1.)

332 (Note 2.)

°C/W

Junction and Storage

Temperature Range

TJ, Tstg

–55 to +150

°C

1. FR–4 @ Minimum Pad

2. FR–4 @ 1.0 x 1.0 inch Pad

http://onsemi.com

PNP SILICON

BIAS RESISTOR

TRANSISTORS

SC–70/SOT–323

CASE 419

STYLE 3

Preferred devices are recommended choices for future use

and best overall value.

3

2

1

PIN 3

COLLECTOR

(OUTPUT)

PIN 2

EMITTER

(GROUND)

PIN 1

BASE

(INPUT)

R1

R2

MARKING DIAGRAM

6x = Specific Device Code

x

= (See Marking Table)

M = Date Code

6x M

DEVICE MARKING INFORMATION

See specific marking information in the device marking table

on page 2 of this data sheet.

相关PDF资料 |

PDF描述 |

|---|---|

| MUN5135T3 | 100 mA, 50 V, PNP, Si, SMALL SIGNAL TRANSISTOR |

| MUN5130T3 | 100 mA, 50 V, PNP, Si, SMALL SIGNAL TRANSISTOR |

| MUN5111T3 | 100 mA, 50 V, PNP, Si, SMALL SIGNAL TRANSISTOR |

| MUN5115T3 | 100 mA, 50 V, PNP, Si, SMALL SIGNAL TRANSISTOR |

| MUN5135T3 | 100 mA, 50 V, PNP, Si, SMALL SIGNAL TRANSISTOR |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MUN5138T1G | 制造商:ON Semiconductor 功能描述:PNP DIGITAL TRANSISTOR (B - Tape and Reel 制造商:ON Semiconductor 功能描述:Transistors Switching - Resistor Biased PNP DIGITAL TRANSISTOR |

| MUN5140T1G | 制造商:ON Semiconductor 功能描述:PNP DIGITAL TRANSISTOR (B - Tape and Reel 制造商:ON Semiconductor 功能描述:REEL / PNP DIGITAL TRANSISTOR (B |

| MUN5141T1G | 制造商:ON Semiconductor 功能描述:PNP DIGITAL TRANSISTOR (B - Tape and Reel 制造商:ON Semiconductor 功能描述:REEL / PNP DIGITAL TRANSISTOR (B |

| MUN51XXDW1T1 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:Dual Bias Resistor Transistors |

| MUN51XXT1 | 制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:Bias Resistor Transistor |

发布紧急采购,3分钟左右您将得到回复。